您现在的位置是:首页 >其他 >Microelectronic学习章节总结(3)-- gate level to physical level design网站首页其他

Microelectronic学习章节总结(3)-- gate level to physical level design

文章目录

PPT:13,14-a,15-1,15-b,16

数字逻辑设计的主要流程

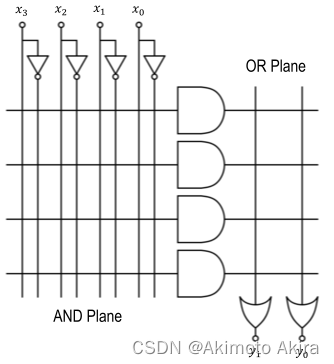

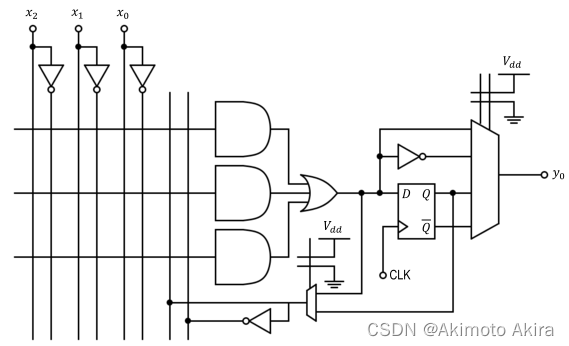

IC设计主要有分为两个阵营:一是ASIC(application specific intergrated circuit),另一个阵营是FPGA(field programmable gate array)。其都可用HDL进行设计,但是实际实现方法是有不同的。其中ASIC更频繁地使用在有大规模生产的特定功能的场景下,而且一旦设计和验证流程走完后电路的逻辑和性能就完全固定,生产的流水线也固定下来。然而FPGA的通用性更强,通过对逻辑门阵列中逻辑门电路之间链接的修改实现一些特定功能,这种方法下,电路的结构很容易修改,应用场景也更多变,但是自由度的增加带来的是性能的降低和价格的升高。因此FPGA很多时候用于ASIC芯片制造之前的逻辑仿真或者原型机的试运行。FPGA的前身是PLA(programmable logic array)如图fig1所示,其通过链接and plane和or plane输入线上的交叉点来进行逻辑表达(图中是简化示意图,与门和或门上的输入信号线实际有两根以上,也就是说需要连接两个以上的交叉点来将输入补充好),这种方式的主要思想是用and, or, not三种逻辑门来表示所有可能的逻辑关系,此外通常为了表达时序电路,在输出端还会增加D flip-flop回馈电路如图fig2所示。

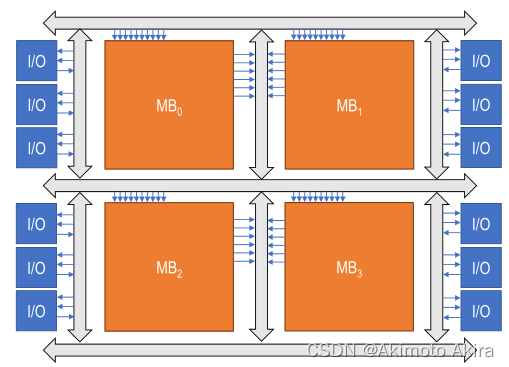

上面的电路表示的仅仅是一个Macrocell,由多个Macrocell可以组合成一个Macroblock用于实现更加复杂的功能,多个Macroblock通过总线想连输出到外部IO口就构成了CPLD(Complex Programmable Logic Device)的基本结构,如图fig3所示。

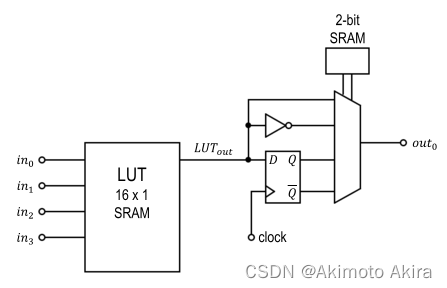

但在FPGA中使用的是look-up-table来表示逻辑,这种方法的好处在于用户可根据实际的应用场景生成的真值表来直接定义FPGA的功能,其结构如图fig4所示,其中SRAM也可以替换其他种类可读写的memory例如EEPROM,同样上面的CPLD结构也适用于FPGA。

对于ASIC电路从设计到市场主要有下面的流程:

- 逻辑设计(logic descroption):用HDL对电路的逻辑行为进行描述

- 预综合(Pre-synthesis):根据HDL描述生成一个netlist,这个netlist中不包括任何时序或者其它性能上的描述,仅仅转换为gate-level description。

- Mapping:使用定义了实际元件的元件库与generic gate-level description中的元件进行匹配,并且使用算法对结构进行优化分析,并产生post synthesis netlist(主要是STA(Static analysis)和power analysis),这一部分主要使用Synopsys Prime Time来完成。其可以生成Post-synthesis report。这里主要包括了3个部分:Area report, Timing report, Power report

- 布局(Placement):将上面生成的post synthesis netlist 中的元件放到power ring(可以理解为片上电源和地组成的线路)中

- 布线(routing):如名所示需要将元器件之间的逻辑连接给连起来,另外也需要确定连线的metal layer。

- 封装(packaging):将内部网络与封装上的Pads连接

- DRC-验证(Design rule check verification):这个验证中包括了area, timing, power, crosstalk noise, power supply noise, electromigration, process variations influence on performace的规格验证。

实际上在整个流程中还有很多其它的验证环节用于保证产品的逻辑功能符合要求,以及在制造环节中得到较低的不良率,这些内容在Testing and fault tolerance中再进行详细描述。

logic family

这一章节实际上讨论的是VLSI集成逻辑电路(或者说是逻辑门)的实现方式。最初的实现方式是由vacuum tube(电子管)通过磁控制其开关动作实现的。直到贝尔实验室发明了晶体管和后来Schockley发明了双极性三极管之后才开始有了用晶体管实现的逻辑电路。第一个比较成功的IC logic family是TTL(transistor-transistor logic),而第一个纳米级别集成度的logic family是ECL(Emitter-Coupled Logic)。然而单晶体管的巨大消耗使得其集成度受到限制,从而logic family的重心从双级型晶体管移到了MOSFET。第一个MOS logic family就是CMOS。

CMOS

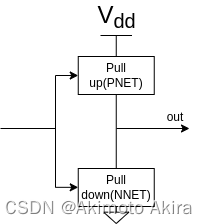

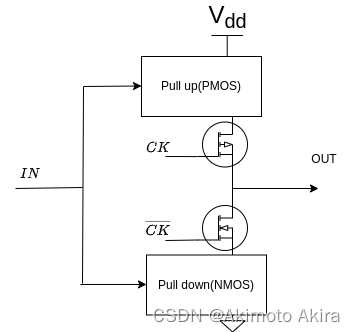

MOSFET中PMOS和NMOS是两种逻辑相反的晶体管(在G极施加同样的信号其开关状态相反),例如当G为高电平时,NMOS开启,PMOS关断。CMOS电路的主要结构示意图如fig5所示,上下两个逻辑块对于同样的输入输出的逻辑结果是互补的。由于NOMS的和PMOS的导通特性,NMOS逻辑更适合低端导通而PMOS更适合高端导通,因此在COMS中上拉为PMOS逻辑而下拉则是NMOS逻辑。

NMOS的一阶电流公式为: I D = K × W L × ( ( V G S − V t h ) × V M I N − V M I N 2 2 ) I_D=K imes frac{W}{L} imes ((V_{GS}-V_{th}) imes V_{MIN}-frac{V_{MIN}^2}{2}) ID=K×LW×((VGS−Vth)×VMIN−2VMIN2),其中 V M I N = m i n [ V D S , V G S − V t h ] V_{MIN}=min[V_{DS}, V_{GS}-V_{th}] VMIN=min[VDS,VGS−Vth],且对于NMOS而言:

- 当 V G S < V t h V_{GS} < V_{th} VGS<Vth 时,截止区(夹断电流)。

- 当 V G S > V t h V_{GS} > V_{th} VGS>Vth 且 V D S < V G S − V t h V_{DS} < V_{GS} - V_{th} VDS<VGS−Vth 时,变阻区。

- 当 V G S > V t h V_{GS} > V_{th} VGS>Vth 且 V D S > V G S − V t h V_{DS} > V_{GS} - V_{th} VDS>VGS−Vth 时,饱和区(导通DS)。

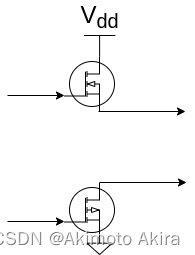

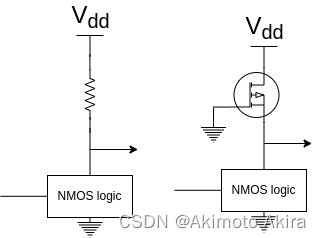

当NOMS用于传输高电平时,我们知道此时DS是导通的,由于MOS管在导通时 V D S → 0 + V t h V_{DS} ightarrow 0+V_{th} VDS→0+Vth(管压降),从而会导致S极的电平被拉高到趋近VDD此时因为 V G → V D D V_{G} ightarrow VDD VG→VDD所以这种情况下反而会使MOS管电流减小到截止。因此,NMOS不适合高端驱动。同样的道理,PMOS相反,当作为低端驱动时,会将 V D V_{D} VD(输出端口)下拉到低电平导致MOS管截止,因此PMOS不适合低端驱动。下面的图为NMOS高端驱动核PMOS低端驱动的电路。

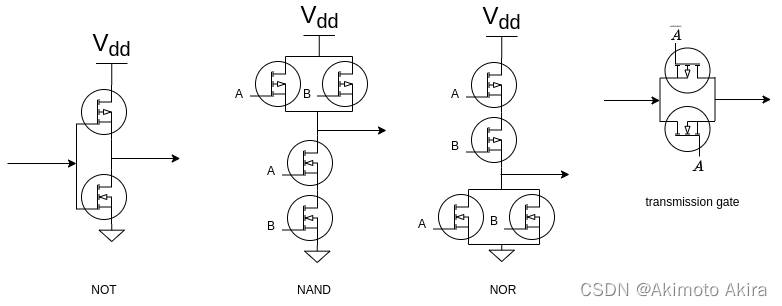

根据此实现的基本逻辑电路如图fig6所示,需要注意的是transmission gate,这个是由于单个MOS管的传送PMOS在传输信号1时会比0慢,NMOS传输0比1慢,这个电路可以实现用PMOS传输1用NMOS传输0,此外其它的逻辑门都可以用这几种实现来进行组合:

对于这个Transistor gate我们知道在多个串连的情况下其传输的电压是有损耗的(管压降),因此通常为了保持电压会在多个串连的transistor gate之间加上两个NOT门逻辑电路来拉高电压。

Transistor实现的时序逻辑

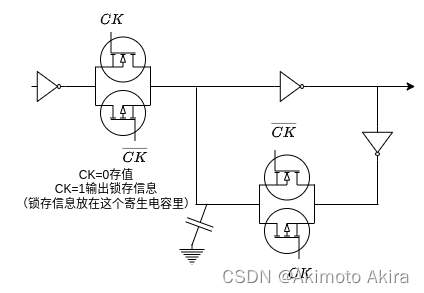

下图fig8为使用transistor gate实现的锁存器和由锁存器构成的D-flip-flop。

PSUDO-NMOS

图fig9是pseudo-NMOS电路的结构,其在CMOS的基础上用一个电阻替代了PMOS构成的上拉部分,这样可以减少电路所占的area,但是其功耗会有所增加因为在NMOS开启时由于不是完全关断还是会有电流流过电阻,进一步的解决方法是将电阻替换成一个常开的PMOS,这样可以进一步减小area同时由于其电阻值较小,在这个PMOS上的功耗也会更小,但是这会同时影响到dynamic和static power dissipation。此外其输出在低电平时不能到完全为0电平。但是速度会比CMOS更快一点

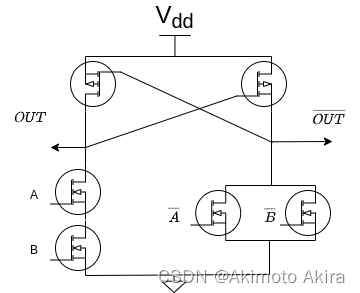

DCVSL(Differential Cascode Voltage Swing Logic)

输入时输出的结果帮助关段或开启PMOS,使得开关频率更高

pro:

- 减小了瞬间短路引起的功耗

- 信噪比高(有反向互补输出)

con:

- 网络复杂,area巨大

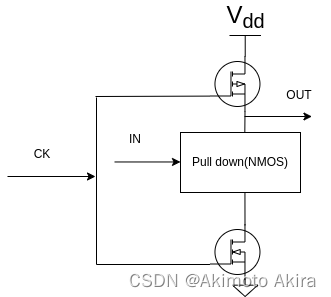

DOMINO

PMOS开启时给负载充电;NMOS开启时根据下拉NMOS电路逻辑决定是否放电,这个周期里读取电路的逻辑值

pro:

- 比CMOS快

- area更小

- 没有短路电流消耗

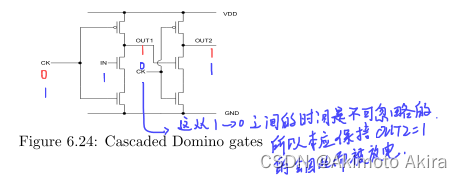

con:

- 在级连时(cascaded domino logic),会有Charge Sharing的问题。由于后一级输入的延迟,clock在后一级输入信号到达之前就打开了NMOS通道放电会导致信号错误(本来要保持高电平但是延迟导致了放电成了低电平),解决方法在输出端加上一个反向器

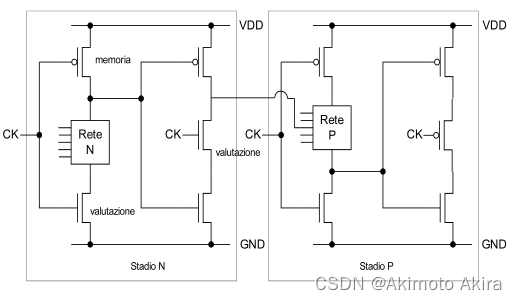

C2MOS(Clocked CMOS)

pro:

- 没有leakage power

- 很快

- 直连电源和地,负载驱动能力很好

con:

- 需要 C K ‾ overline{CK} CK信号,这个信号要CK完全同步

TSPC(True Single Phase Clocking)

Transistor behavior

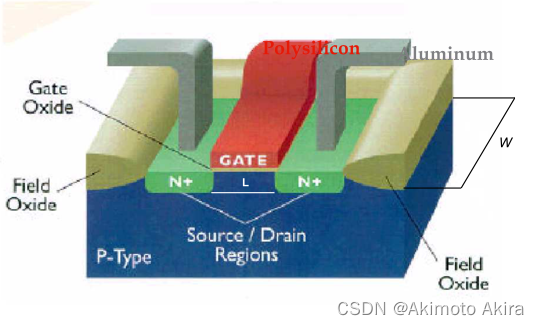

上面讲的一部分NMOS和PMOS的特性这里就不再重复了,这一部分里主要讲有关寄生电容的东西以及一些可以用来分析电路中问题的底层逻辑。对于单个MOS晶体管,其结构如下fig14所示,与其到点性能有关的物理量有以下几个,这也是在工艺设计中能够影响电路性能的晶体管参数:

- L:沟道长度,决定了晶体管从截止区到饱和区状态变化所用的时间,L下降,开关频率增加

- W:沟道宽度,决定了从D到S的电流大小,W下降,电流下降

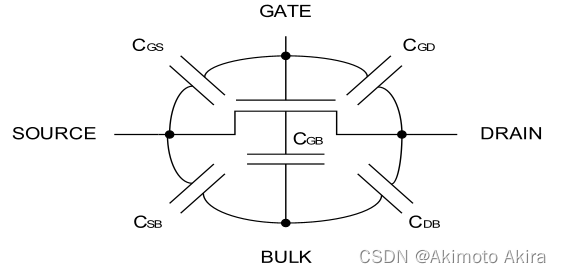

除此之外,我们还要关注的是晶体管各个引脚之间的寄生电容,这些也会成为影响晶体管开关性能的因素。在晶体管引脚之间的寄生电容如图fig15所示,其大小是由晶体管自身的尺寸决定的,即上面提到的W和L,当晶体管本身的尺寸越大,一般来说寄生电容也会越大,例如 C G B = ϵ t o x ⋅ W ⋅ L C_{GB}=frac{epsilon}{t_{ox}}cdot Wcdot L CGB=toxϵ⋅W⋅L,其中 ϵ epsilon ϵ为电介常数, t o x t_{ox} tox为gate上二氧化硅层的厚度。

CMOS inverter案例分析

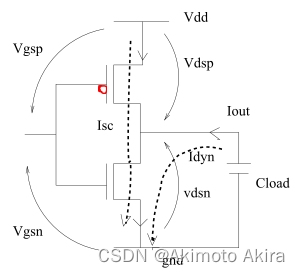

inverter的电路如fig16所示。需要考虑的指标有下:

- Vin:输入信号

- Vout:输出信号

- Idsn:流经NMOS的DS极的电流

- Idsp:流经PMOS的DS极的电流

- Iout:输出电流

其中输入信号的例子是0->1,因此输出信号应当为1->0。另外需要明白的是这里的负载实际上包括了三个部分:

- inverter自身的管压降带来的负载

- 接在输出端口负载本身

- inverter和负载之间连接的负载

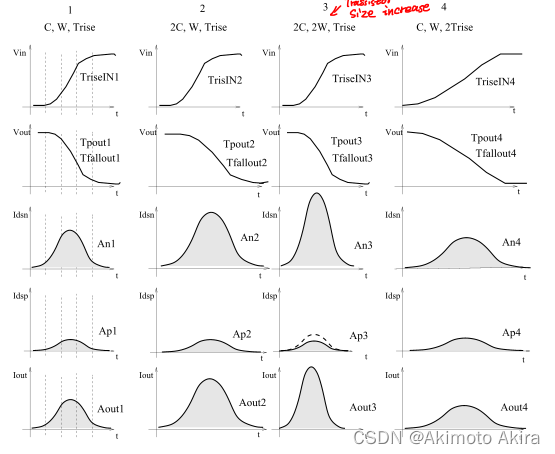

根据电路分析可知: I d s n = I o u t + I d s p I_{dsn}=I_{out}+I_{dsp} Idsn=Iout+Idsp,在这里我们改变负载大小C、晶体管的沟道尺寸W和输入信号上升时间 T r i s e T_{rise} Trise可以得到下面的图表,由此可知

- 负载大小影响晶体管状态转换时的短路电流,

- 沟道变宽实际上可以减少短路的时间,但是会增加短路的峰值电流大小,但是总的功率损耗大致不变(2,3的输出电流面积大致相等)

- 输入信号的延迟会导致短路时间拉长,但是不会影响到输出端的功率消耗(1,4的 I o u t I_{out} Iout面积相等)

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结