您现在的位置是:首页 >技术交流 >FPGA设计之控制集优化详解网站首页技术交流

FPGA设计之控制集优化详解

目录

一、前言

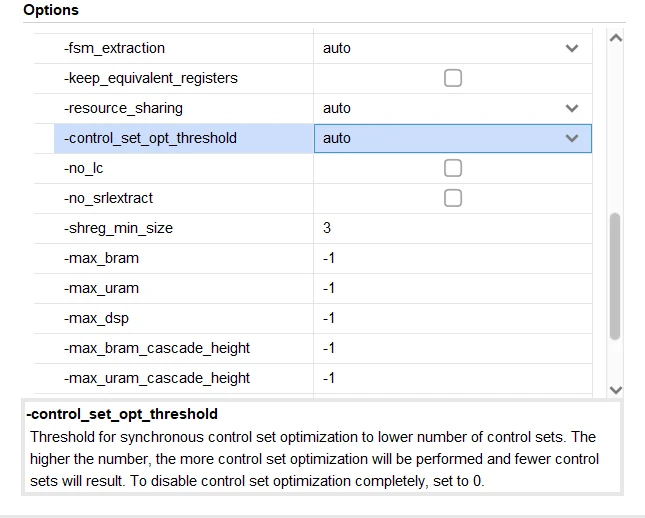

在工程设计优化中,综合阶段优化中有一项常见的优化,控制集(control set)优化,在vivado的Synthesis中有对该配置项的解释,如下图

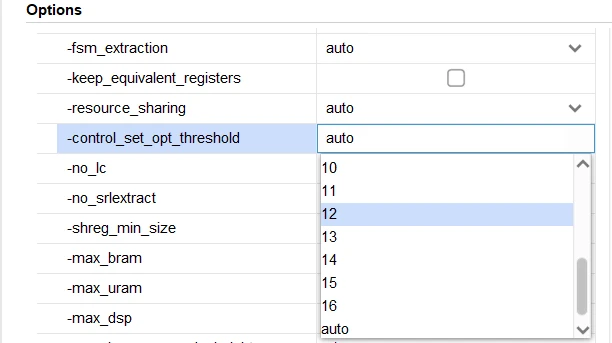

大意为该配置项为触发器的同步控制集门限设置,默认值为auto,也可设置为0-16之间的其他数字,数字设置的越大,优化的控制集将更多,最终存在的控制集将更少,设置为0表示不进行优化。

二、Control Set控制集

控制集即为触发器控制信号的集合,触发器的控制信号包括时钟信号,使能信号,置位/复位信号。以器件xc7vx485tffg1157-1为例,Slice的结构如下图,右侧8个为寄存器。因为一个Slice只有一路的CK信号,一路CE信号,一路SR信号输入,因此,在一个Slice中的FF是共用CK,CE,SR信号,也只有FF使用相同的CK,CE,SR信号才能放置到同一个Slice中。

三、Control Set控制集优化

对控制集的优化也即是根据设置的Control_set_opt_threshold值调整的控制集的数量,通过第二章可知,如果控制集的信号完全相同的寄存器,可放入同一个slice中。设置了控制集优化后,对于一些同步复位,同步置位和同步使能信号,当数量小于设置的Control_set_opt_threshold值时,也可以放置到同一个slice中。

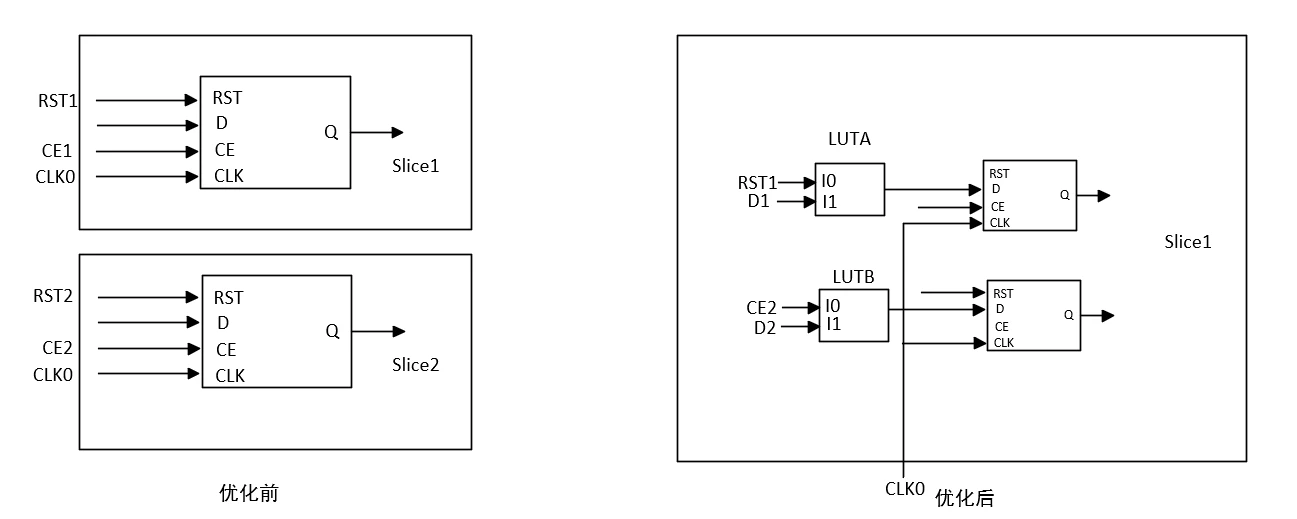

下图中,左侧中是两个处于两个Slice中的寄存器,一个是同步复位,一个是同步使能,二者的时钟信号都是clk0,。通常情况因为两个寄存器的复位和使能信号不同,因此放置在两个slice中。设置优化后,复位和使能信号都是通过前面添加一个LUT来实现同步复位和同步使能的作用,对应寄存器的RST和使能端口不用。

为何前面增加使用一个LUT可以实现同步复制或同步使能的效果?以同步复位为例。

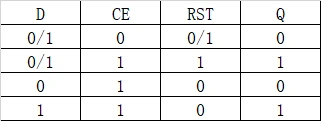

假设原先直接使用寄存器的RST信号输入时,寄存器数据输入D和RST信号的逻辑真值表如下,使能信号高电平时有效,复位信号RST高电平复位,即只有在使能信号高电平,复位信号为低电平时,输入才有效,表中0/1表示为0或1。

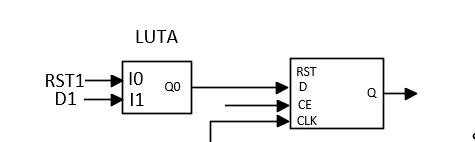

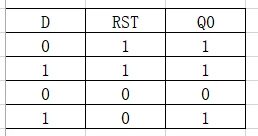

优化增加了LUT后,通过LUT的INIT值来控制同步复位,寄存器的输入D1和复位信号RST1是连接到了LUT的I0和I1输入口,LUT的输出为Q0,即只要保证Q0与D1和RST1的逻辑真值表如下表。即只要RST为1时,LUT的输出Q0为1,RST为0时,输出等于输入D1,即保证了复位信号RST的有效性。下述逻辑最终是在LUT的INIT值上体现。

四、优劣

通过第三节的分析可知,优化后的寄存器放置到了同一个Slice中,在时序上可能会有一定的提高作用,缺点也是显而易见的,需要消耗更多的LUT资源。

根据xilinx的经验,当工程的控制集小于整个芯片控制集数目的7.5%时,可以无需优化,当大于整个芯片控制集数目的15%时,需要降低控制集数目。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结