您现在的位置是:首页 >技术杂谈 >DDS基本原理与FPGA实现网站首页技术杂谈

DDS基本原理与FPGA实现

DDS基本原理与FPGA实现

定义:DDS是指DDS信号发生器,采用直接数字频率合成技术。是一种新型的频率合成技术,具有相对带宽大,频率转换时间短、分辨率高和相位连续性好等优点。较容易实现频率、相位以及幅度的数控调制,广泛应用于通信领域

DDS的经典应用场景:通信系统里调制解调

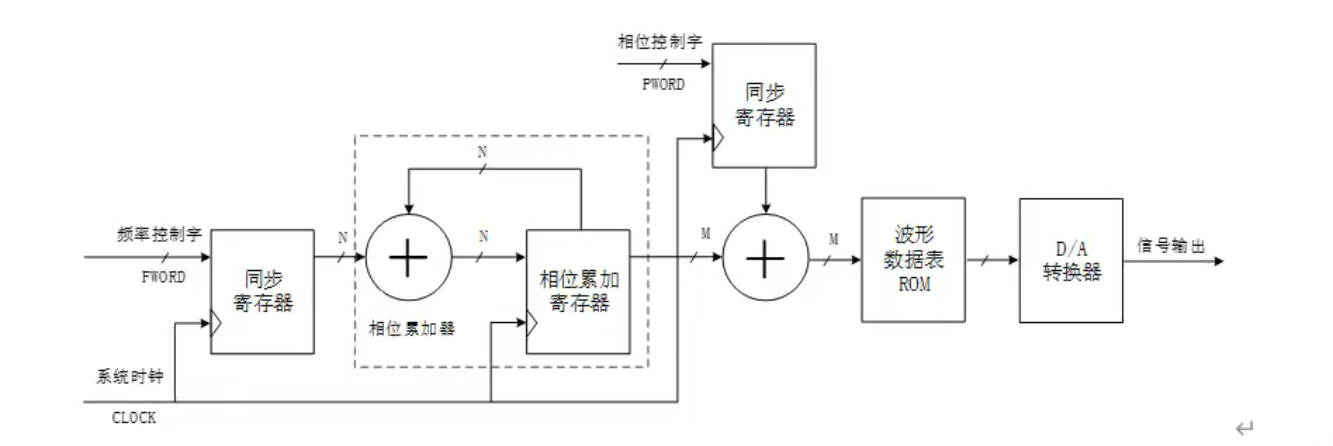

1.系统结构图和理论

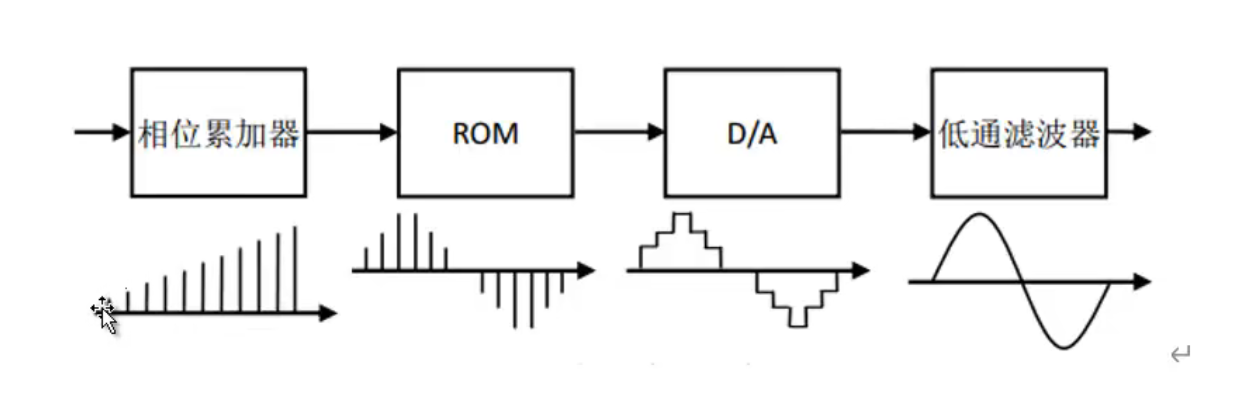

其中相位累加器由N位加法器与N位寄存器构成。每个时钟周期的时钟上升沿,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。

相位累加器输出的数据就是合成信号的相位 。相位累加器的溢出频率,就是DDS输出的信号频率相位累加器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换。波形存储器的输出数据送到D/A转换器,由 D/A转换器将数字信号转换成模拟信号输出。

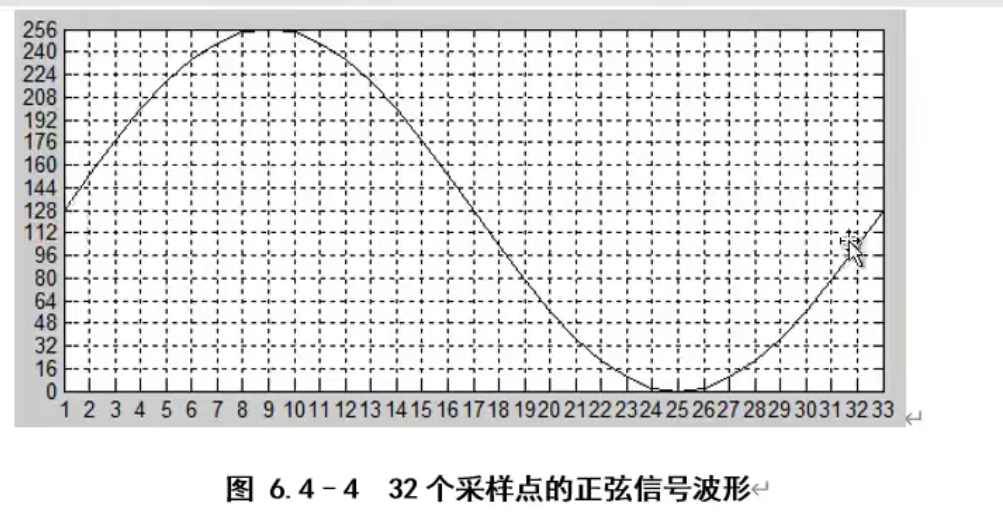

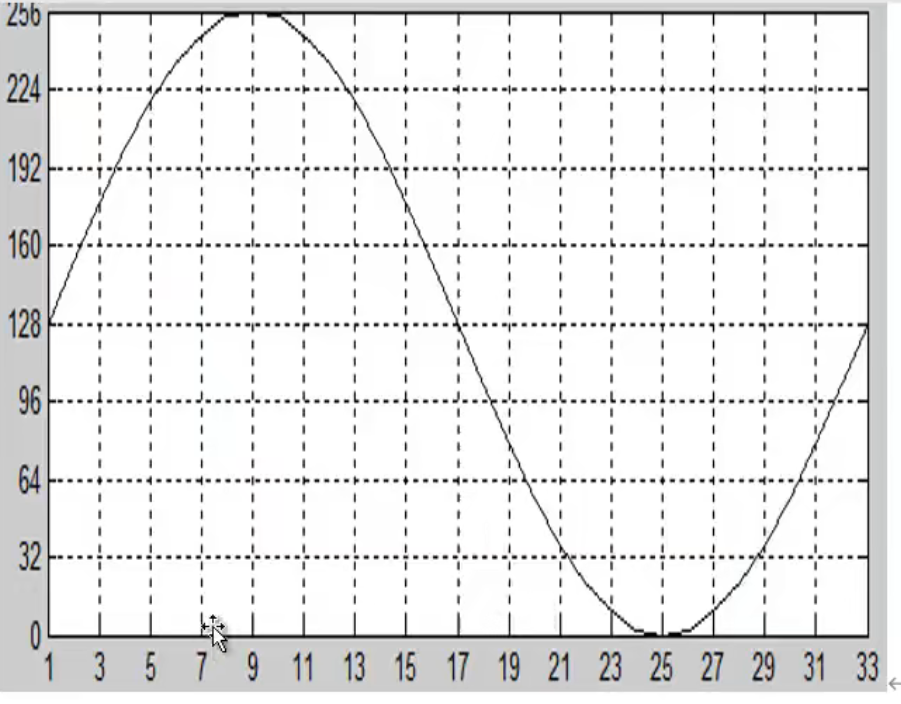

频率1000/32 Hz是由计算公式f=1s/T得来的,其中T的单位也是s,输出完整的一个波形需要32个点,每个点输出需要1ms,因此周期T=32×1ms×0.001=0.032s,因此f=1s/0.032=1000/32 Hz

图6.4-5 16个采样点的正弦信号波形

公式讲解:

(1)当时钟频率Fclk=1000Hz(即时钟周期为1ms使),取点的间隔是1ms,此时输出频率Fo是多少?

Fo = 1000/32,其中32等于2^N,N=5;

Fo=Fclk/2^N

(2)希望输出的频率翻一倍,即输出的点由32个变为16个,取点间隔变为2

Fo = (1000×2)/(32÷2),其中32等于2^N,N=5;

Fo=Fclk/(2^N/2)

(3)希望输出周期为64ms,即输出的点由32个变为64个,取点间隔变为0.5.

Fo = (1000×2)/(32÷0.5),其中32等于2^N,N=5;

Fo=Fclk/(2^N/0.5)

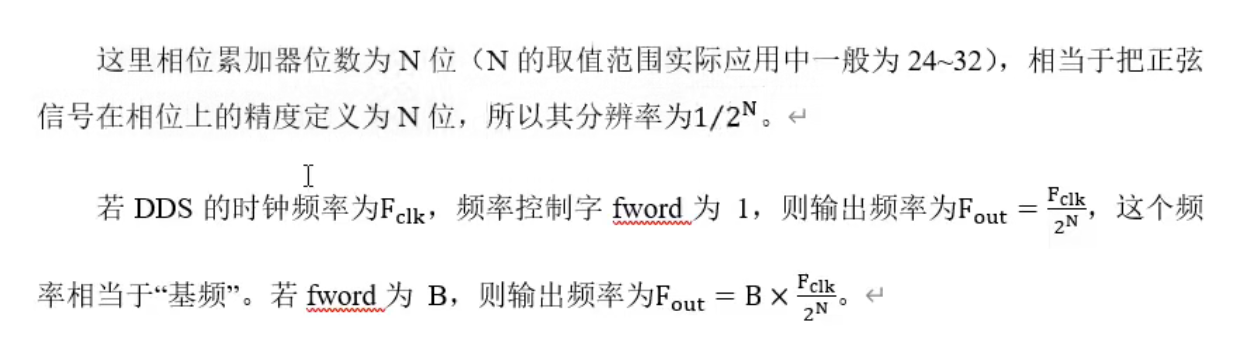

公式总结:

输出频率由频率控制字Fword(也可以用B来表示)来决定,可以表示为:

Fo=Fclk/(2^N/Fword),也可以写为:Fo=Fclk/(2^N/B)=(Fclk × B)/(2^N)

2.代码实现

`timescale 1ns / 1ps

module DDS_Module(

Clk,

Reset_n,

Fword, //频率控制字

Pword, //相位控制字

Data //输出数据

);

input Clk;

input Reset_n;

input [31:0] Fword;

input [11:0] Pword;

output [13:0] Data;

//频率控制字同步寄存器

reg [31:1] Fword_r;

always@(posedge Clk)

Fword_r <=Fword;

//相位控制字同步寄存器

reg [31:1] Pword_r;

always@(posedge Clk)

Pword_r <=Pword;

//相位累加器

reg [31:0] Freq_ACC;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Freq_ACC <= 0;

else

Freq_ACC <= Fword_r + Freq_ACC;

//相位累加器与相位控制字的结果输出

reg [31:0] Freq_ACC_out;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Freq_ACC_out <= 0;

else

Freq_ACC_out <= Freq_ACC + Pword_r;

//波形数据表地址

wire [11:0] Rom_Addr;

assign Rom_Addr = Freq_ACC_out[31:20];

blk_mem_gen_0 blk_mem_gen_0_u0 (

.clka (Clk),

.addra(Rom_Addr),

.douta(Data)

);

endmodule

补充说明:

相位控制字就是给地址加一个偏置值,因为波形的值存放在rom当中,只需要改变rom的地址就可以改变波形的相位.

测试代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/04/28 20:32:51

// Design Name:

// Module Name: DSS_Module_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module DSS_Module_tb;

reg Clk;

reg Reset_n ;

reg [31:0] Fword ;

reg [11:0] Pword ;

wire [13:0] Data;

DDS_Module DDS_Module_u0(

.Clk(Clk),

.Reset_n(Reset_n),

.Fword(Fword),

.Pword(Pword),

.Data(Data)

);

initial Clk = 1;

always #10 Clk = ~Clk;

initial begin

Reset_n =0;

Pword = 0;

Fword = 65536;

#201;

Reset_n =1;

#20000000;

Fword = 65536*1024;

#20000000;

Fword = 65536*32;

#20000000;

$stop;

end

endmodule

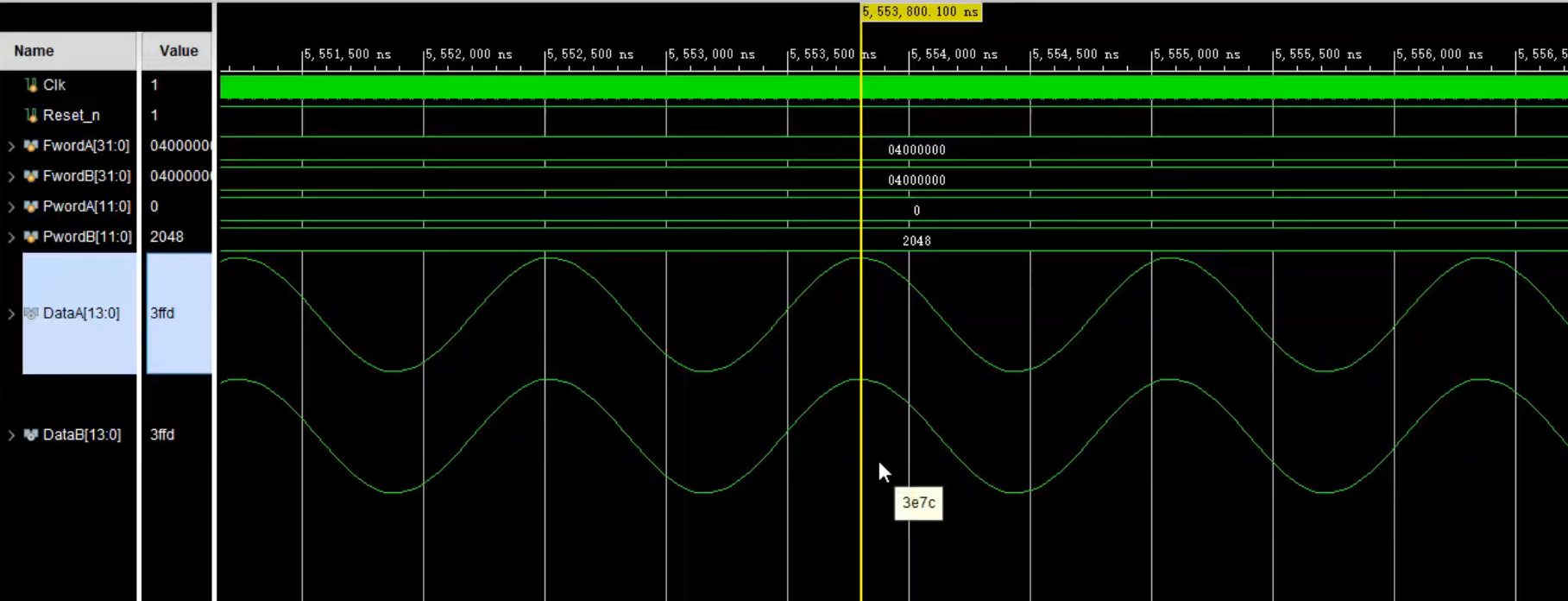

实验结果:

视频链接:22B DDS结构的FPGA实现_哔哩哔哩_bilibili

--晓凡 2023年4月29日于桂林书

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结