您现在的位置是:首页 >其他 >verilog设计实现8b-10b编码器包括3b4b,5b6b 及modelsim仿真网站首页其他

verilog设计实现8b-10b编码器包括3b4b,5b6b 及modelsim仿真

简介verilog设计实现8b-10b编码器包括3b4b,5b6b 及modelsim仿真

下面是8b10b编码器的设计步骤。

-

确定数据输入和输出接口。例如,您需要确定8位并行数据输入和10位串行数据输出。

-

计算数据带宽。这与芯片中可用的时钟速度密切相关。

-

选择编码表。根据应用选择最佳编码表,8b10b编码器至少应使用一张编码表。详细了解和选择编码表有利于改善编码器的性能。

-

编写编码器的状态机。编码器的状态应针对输入数据,在状态转移前确定符号的输出。同样,状态也应该考虑插入或删除代码的位置。

-

关联状态机的输出符号。在每个状态中,都必须关联与该状态相关联的输出符号。此项工作需要根据编码表中编码符号的特点进行。

-

设计电路。设计电路包括选择元件,例如寄存器、计数器、直接构成,以及各种传输门、存储器等。

-

编写Verilog代码。将状态机转换为描述硬件电路的Verilog代码。

-

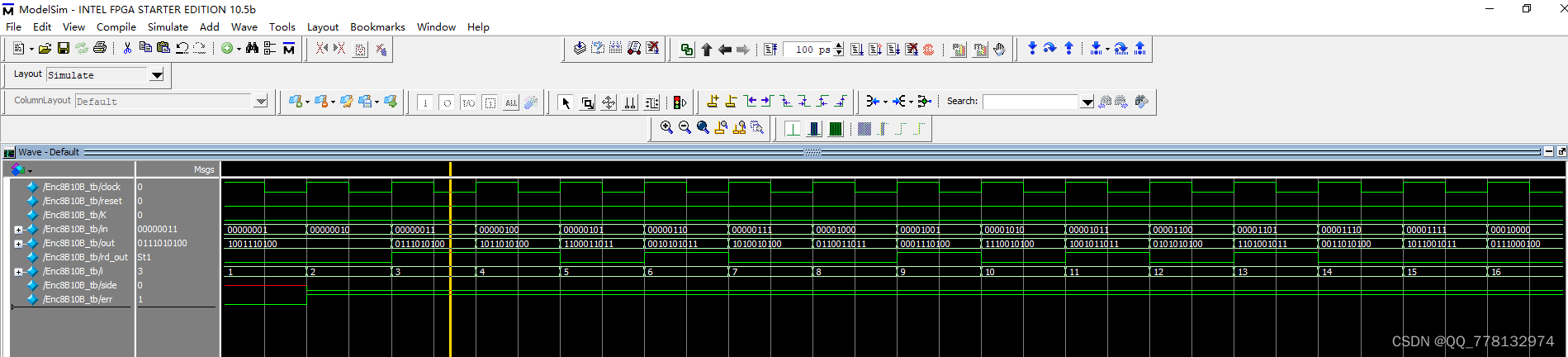

进行仿真测试。使用Verilog开发环境进行仿真测试,并通过仿真验证电路功能。

-

实现和验证。用Verilog将设计转换为FPGA或ASIC的物理实现,并通过测试验证设计性能。

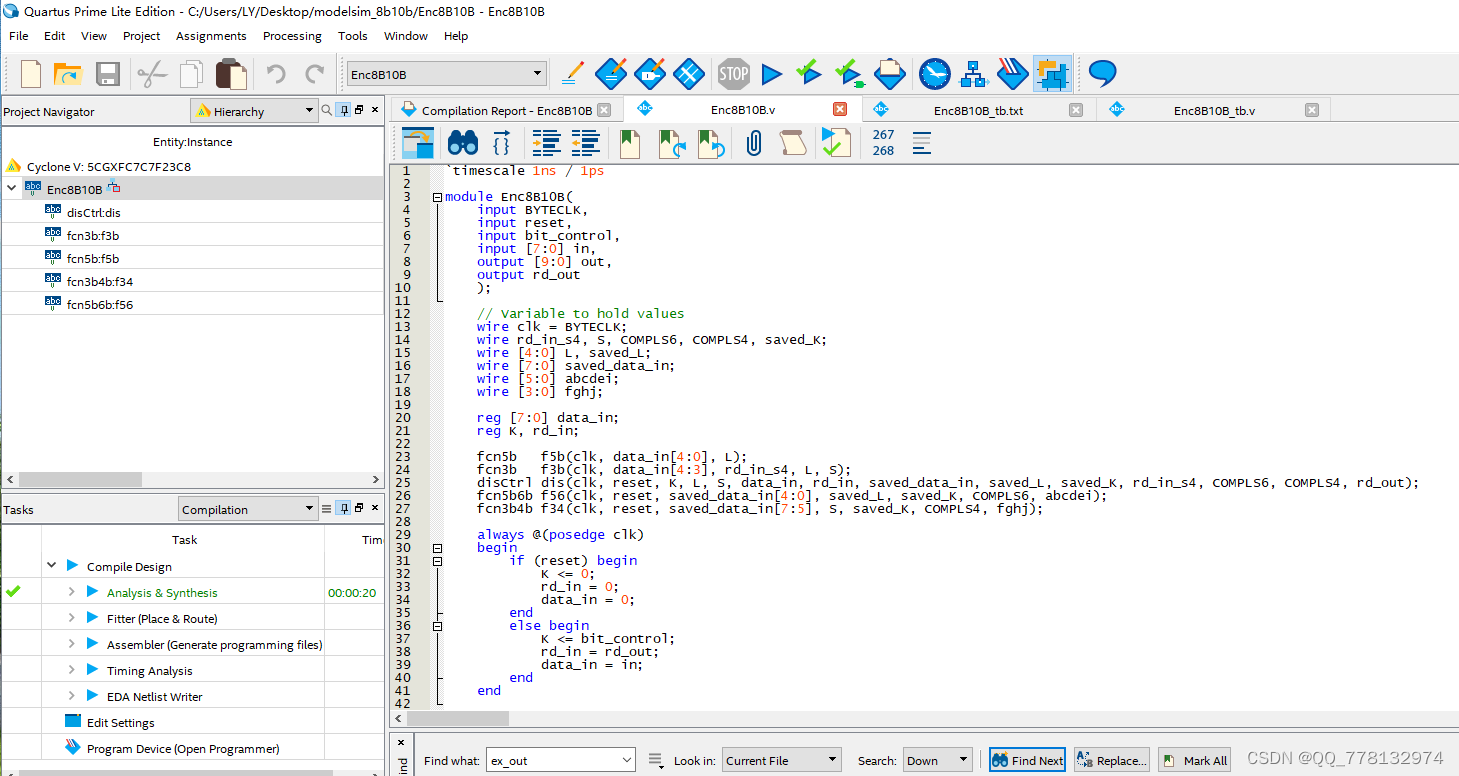

工程截图和仿真截图如下:

顶层模块代码如下:

`timescale 1<风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结