您现在的位置是:首页 >技术交流 >E5--Aurora 8/10Bip核实现光纤接口通信2023-04-22网站首页技术交流

E5--Aurora 8/10Bip核实现光纤接口通信2023-04-22

1.场景

使用两块开发板A和B,通过光纤接口将在A板上ROM中存储的图片数据转发到B板并显示在B板连接的显示屏上,实现光纤接口通信。 具体场景是,由于A735T片上资源有限,因此ROM IP存储了一张1024*600(LVDS屏幕)分辨率图像的1/16,在发送端添加按键,第一次按键按下,将发送这1/16的数据到接收端,第二次按下,发送的则是每个像素取反后的数据,同时接收端每收到一张图片都会发送一个长达2s的“1“,发送端接收到此数据驱动LED亮2s。接收端使用RAM IP作为数据缓存实时更新来自光口的数据,读出端则是根据LVDS驱动模块产生的数据请求信号读出,最后达到的效果是发送端按一次按键,接收端切换一张图片,发送端led亮持续2s。与链接相比,主要的不同在于,实现光口通信可以有多种方式,例如使用快速GT收发器采用万兆以太网协议通信,使用aurora协议(使用GT ip或本文使用aurora协议)GT ip核实现光口通信是使用GT IP核,本文使用auraro IP核实现光纤通信,本质是一样的,使用的硬件环境、实现的效果,连接的方式都是一样的。但具体的实现方式上略有差别。

2.Auraro简介

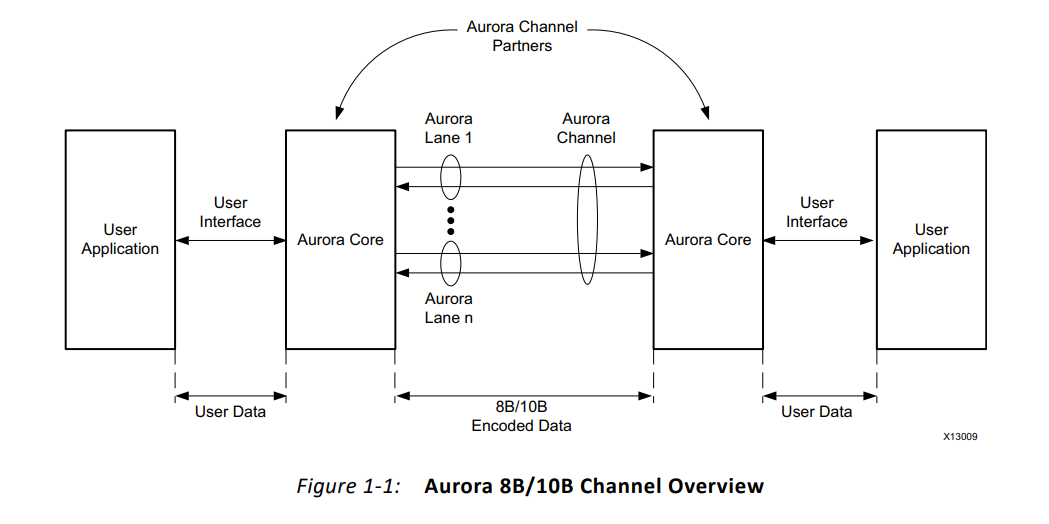

Aurora 接口是Xilinx公司提供的开放、免费的点对点的链路层高速串行总线协议,说白了,就是个并行转串行,然后串行信号用xilinx的高速收发器传输,支持全双工模式,如图所示。支持AXI & ACE总线,Aritx-7、Kintex-7、Virtex-7 families、UltraScale器件、UltraScale+器件支持该协议。

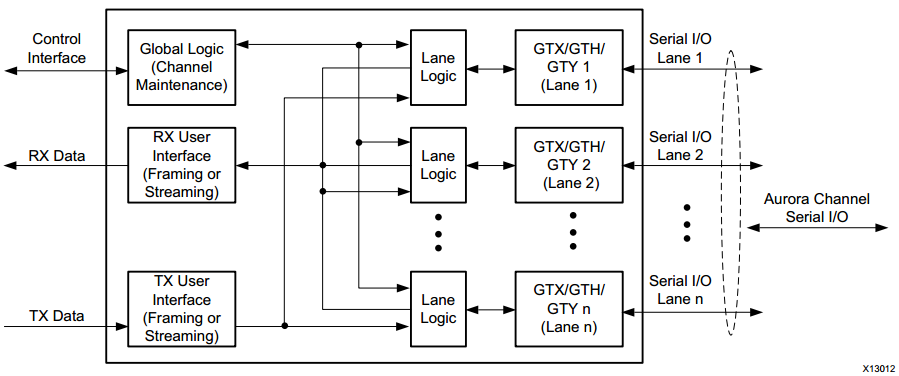

其主要的模块图如下,Aurora 8B/10B核的主要功能模块包括:

Lane Logic: 每条lane都包含一个GT,Lane逻辑模块实体驱动每个GT,并初始化每个GT收发器,处理编解码及错误检测等。从宏观角度理解,这也是该协议最本质的特征。

Global Logic: 全局逻辑模块执行通道初始化的绑定和验证阶段。 在运行过程中,模块生成Aurora协议所需的随机空闲字符,并监控所有lane逻辑模块的错误。

RX User Interface: 接收端用户接口使用AXI4-S接口将数据从channel传到用户应用并可进行接收流控功能。

TX User Interface: 发送端用户接口使用AXI4-S接口将数据从用户应用传到channel并进行发送流控功能。标准时钟补偿模块嵌入在核中。这个模块控制时钟补偿(CC)字符的周期性传输。

此外,aurora定义了物理层的电器接口以及链路层数据的封装方式,加入了流控,初始化的机制,保障了更好的总线效率和传输的准确性。

3.AXI时序

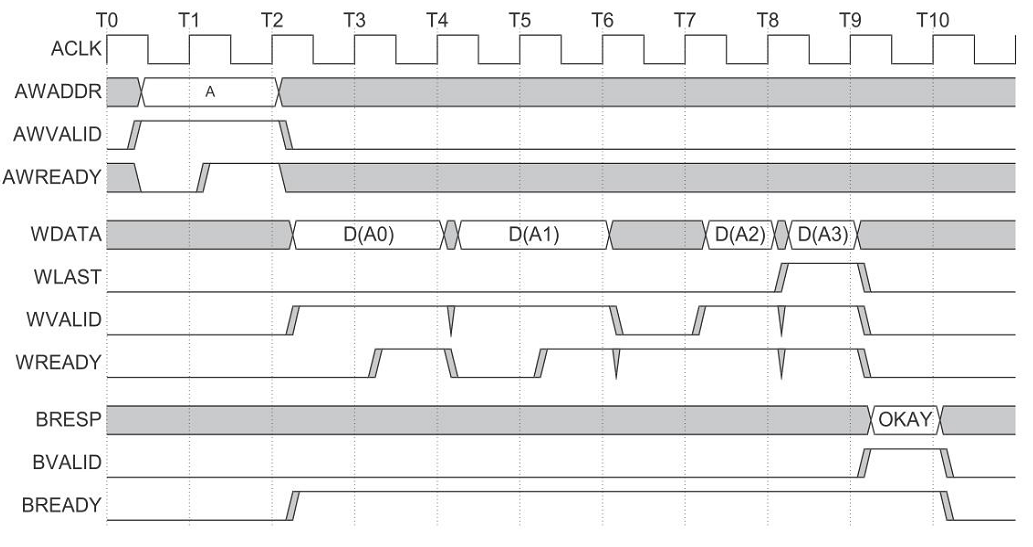

Aurora提供了两种接口形式,一种是streaming,另一种是framing,现在列出streaming接口的读写时序,但工程中配置了framing接口。Aurora接口采用AXI总线面向用户侧,AXI4总线写时序图如下所示。

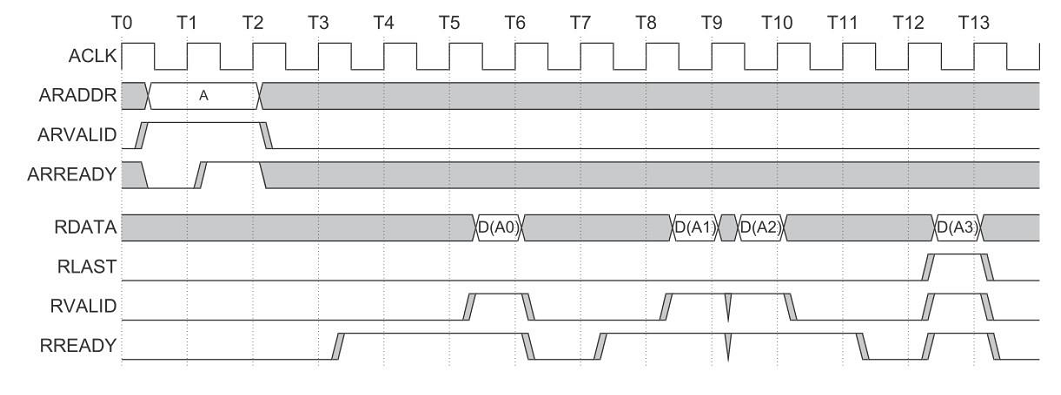

AXI4总线读时序图如下所示

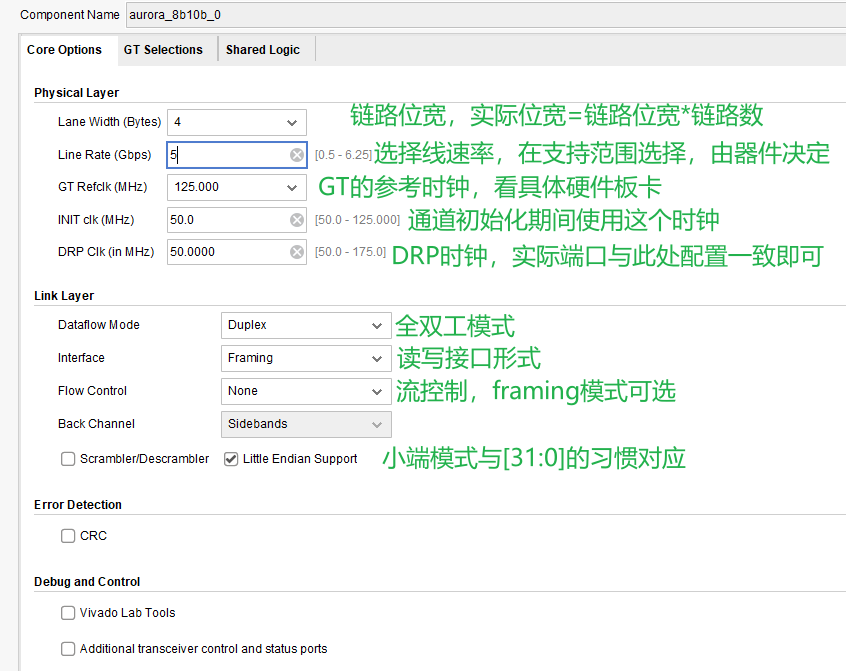

4.关于ip核配置

本例中的配置及其含义已简单说明

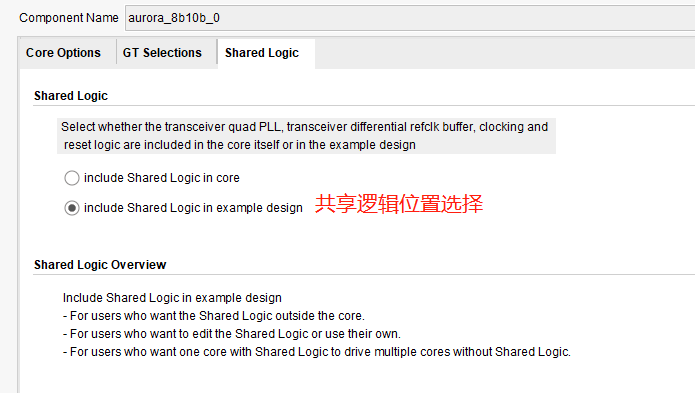

IP核的使用通过example design来完成,这是因为例程中将共享逻辑设计完成,使用时只需要修改部分地方即可。

5.源代码修改说明

①support模块输入的初始化差分时钟改为单端时钟init_clk,从时钟ip核出来;

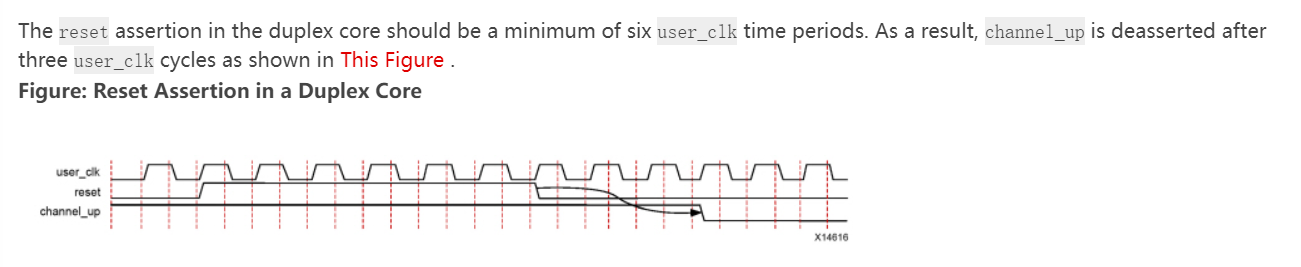

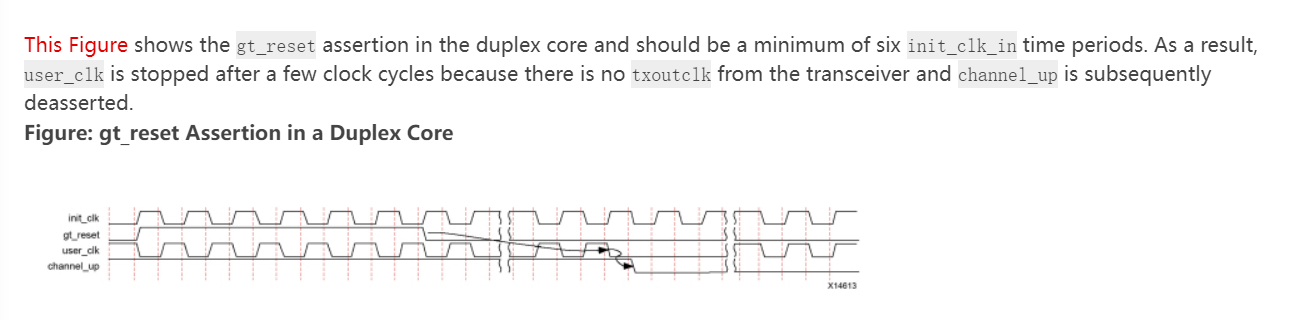

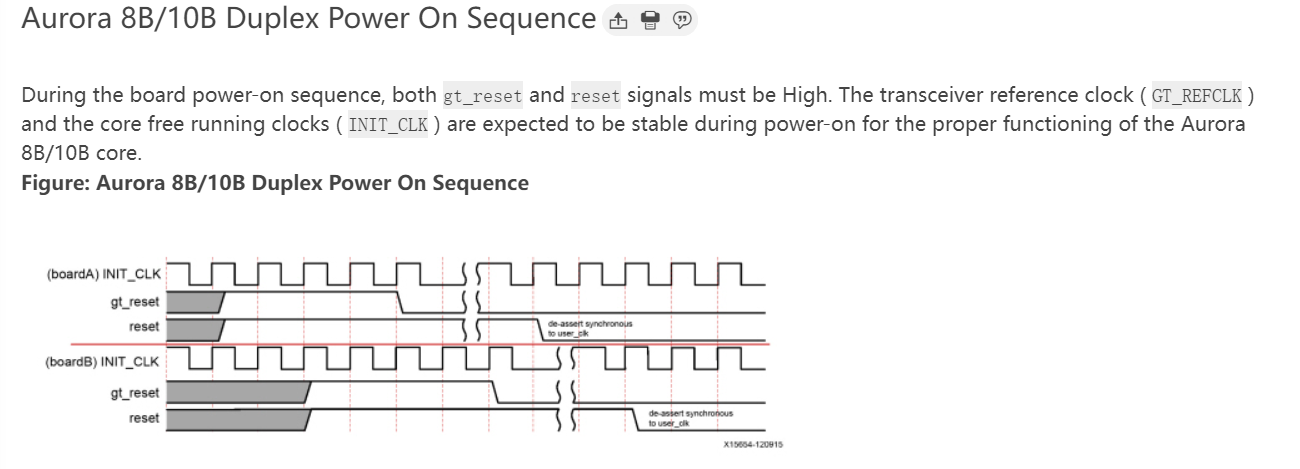

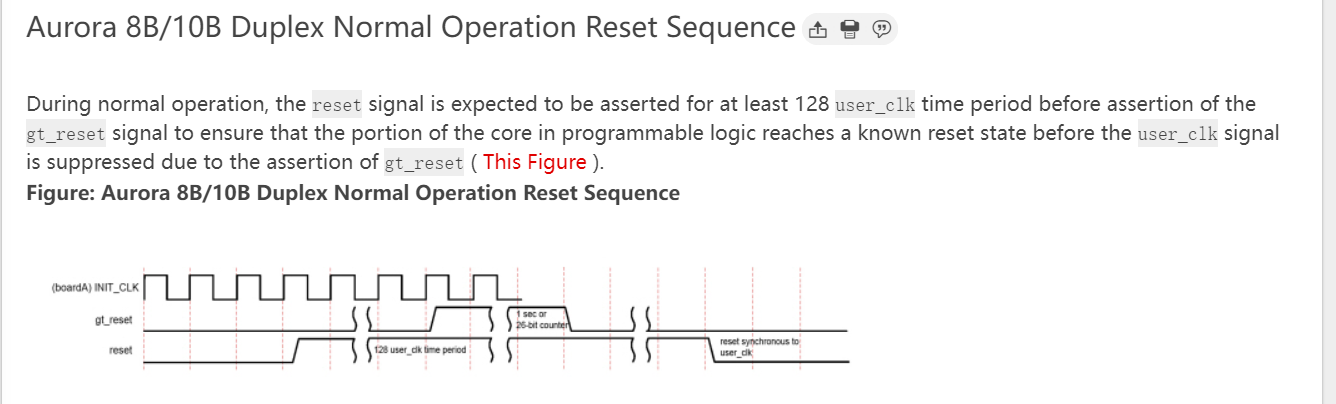

②顶层中的reset信号和GT_reset信号一个是复位ip核,一个是复位GT收发器,这两个信号怎么给需要设计,总归遵循以下要求,如图所示。CHANNEL_UP:置位表示此时对应的channel初始化完成,处于正常工作的状态,lane_up:当对应的Lane初始化完成后,会断言对应的lane_up,根据这两个信号完成复位模块的设计。

Reset信号、gt_reset信号的复位应该至少持续6个时钟周期;

上电初始化时,应该保持高电平,并且gt_reset应该先于reset解复位,并且二者都同步于初始化时钟。

使用过程中做复位操作,应该是reset先于gt_reset至少128个用户时钟,保证在gt_reset复位时,也就是user_clk消失之前,所有的ip进入复位状态,然后gt_reset复位至少持续1sec。

③drpclk由差分改为单端从时钟ip核进入。

④其他ip核端口的设计,power down,高电平有效。当其为高时,GT会进入非工作、低功耗的模式(类似睡眠模式)。我们使用的时候一般直接拉低。此处输入为0。loopback:回环模式,实际使用一般接到0。hard_err:错误表征应信号,主要是硬件类错误。soft_err:错误表征应信号,主要是软件类错误。frame_err:错误表征应信号,主要是帧类错误,可根据实际情况判断将这些信号接到哪里。关于Drp接口除了时钟全部设置为0即可。

⑤设计数据产生模块aurora_tx模块,代码简单清晰,直接参看代码即可。

⑥设计数据接收模块aurora_rx模块,生成有效数据和同步数据信号。代码简单清晰,参看本例工程链接。

⑦关于代码中其他模块的设计,同GT部分。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结