您现在的位置是:首页 >技术交流 >Xilinx之7系列时钟规划失败解析网站首页技术交流

Xilinx之7系列时钟规划失败解析

目录

一 、前言

在设计的工程中,经常会在implementation的布局或布线阶段失败,下面将针对xilinx 7系列时钟规划失败的场景进行分类描述。本文示例器件为xc7k480tffv1156-2L,其他时钟架构类似的可参考。

二、时钟规划

2.1 时钟单元经过非时钟路径

原因:时钟线路某些单元处于非时钟路径上,导致布局失败

示例:将FF的clk约束到普通的pin上

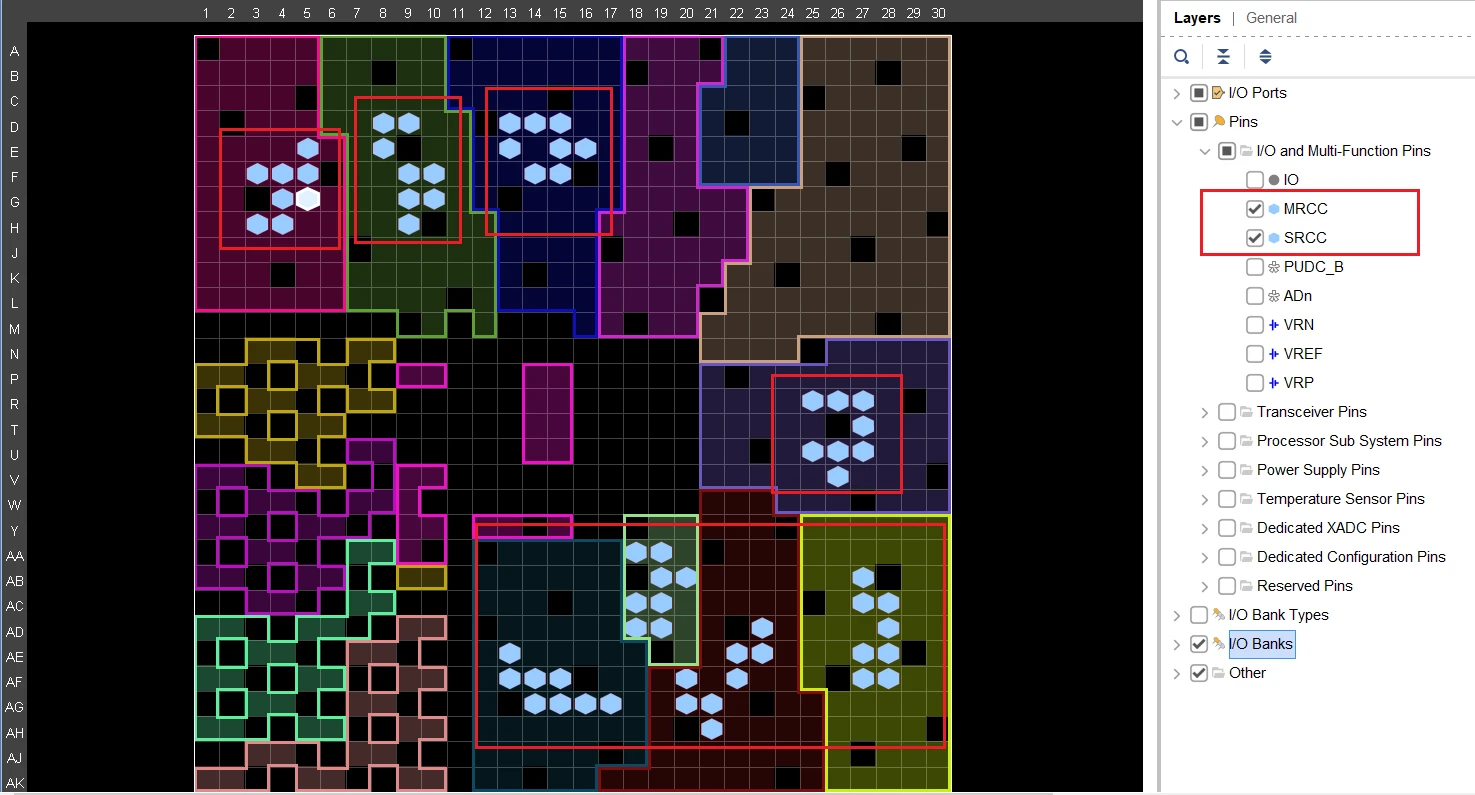

操作:将时钟clk端口约束到非clk 端口上,器件的时钟端口可以在Window->Package上查看,打开右侧设置窗口,进入Layers中,在Pins中勾选MRCC和SRCC,即只显示时钟clk端口,下图左侧红色方框内的灰白色单元即为时钟pin。

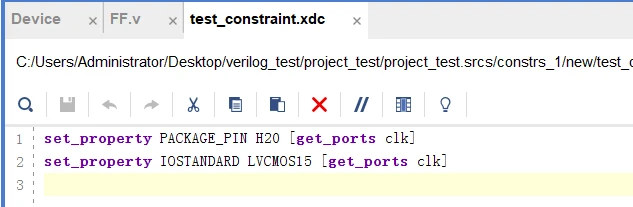

约束文件内容

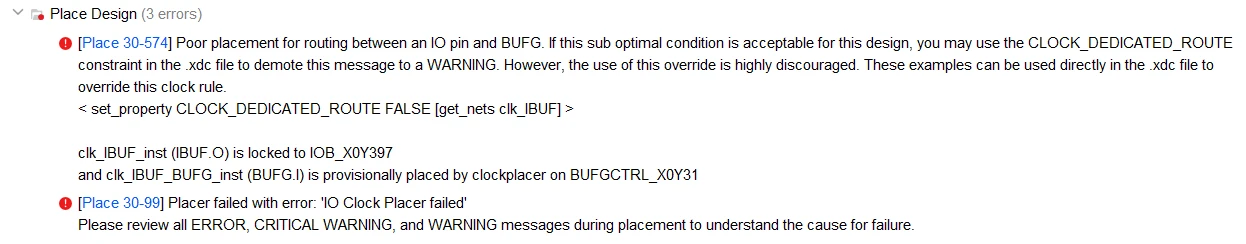

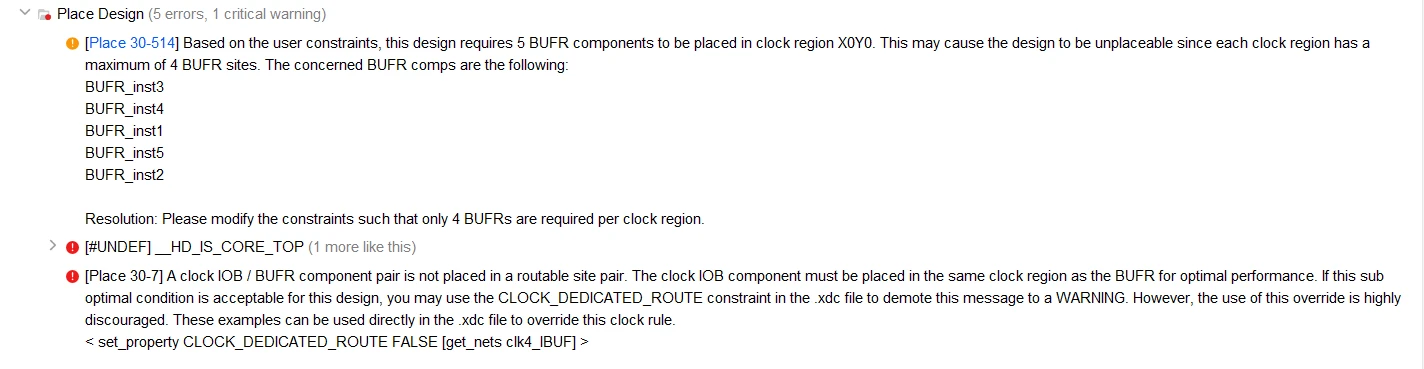

结果:Place Design中报错Place 30-574

解决:将clk约束到时钟pin上即可

2.2 资源不足

资源不足是指时钟缓冲器资源不足,分为时钟区域内IOCKB/RCKB资源不够,芯片的BUFG资源不够,如单个时钟区域内只有4个RCKB,和IOCKB

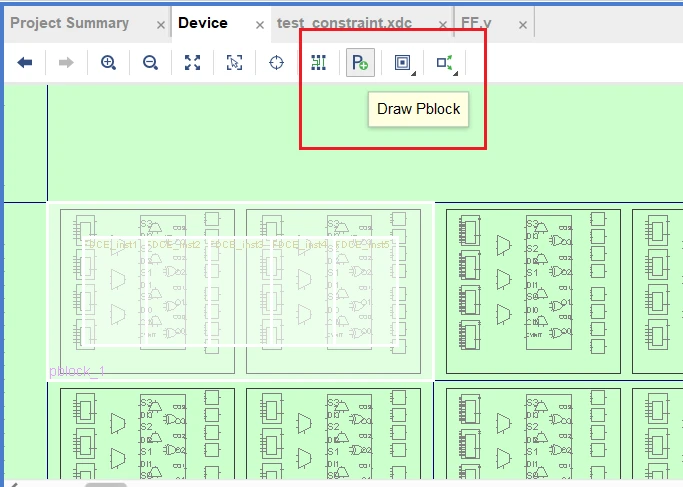

示例:在1个时钟区域内使用5个RCKB,为快速构造场景,使用区域约束Pblock的方式,将连接了5个RCKB的触发器FDCE约束到相邻的一对SLICEL上

操作:通过Device窗口上的Draw Pblock划定区域,在将左侧的Netlists中FF拖入到划定的区域即可。

结果:Place Design报错Place 30-514,内容直接提示超过了可使用的最大BUFR数目4个

解决:重新调整BUFR的位置

2.3 跨半区

原因:全局时钟BUFG和clk约束到不同半区,上半区的BUFG只能被上半区bank的IO 驱动,下半区的BUFG只能被下半区bank 的IO 驱动

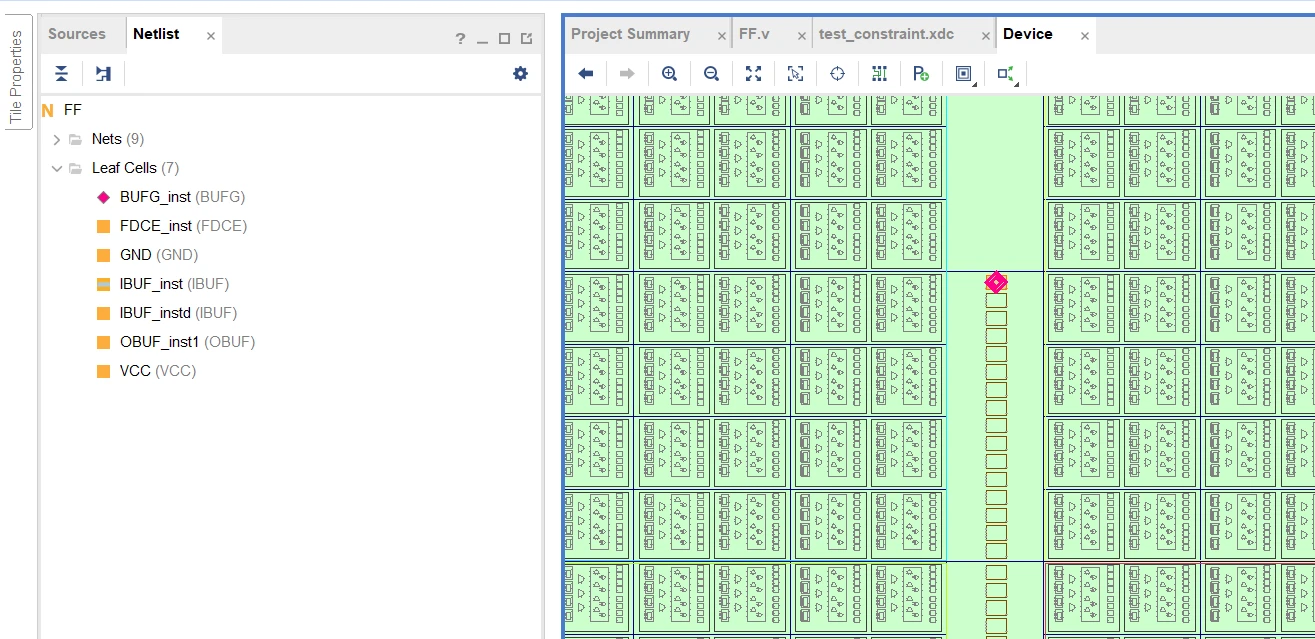

示例:将BUFG和clk分别约束到上半区,上下半区的分界线为水平中间位置,如下图的两个黑色方框范围

操作:将bufg约束到上半区的BUFGCTRL位置,如下图红色菱形标记,将左侧BUFG拖入到右侧Device中的BUFG,clk约束到下半区的IO bank。

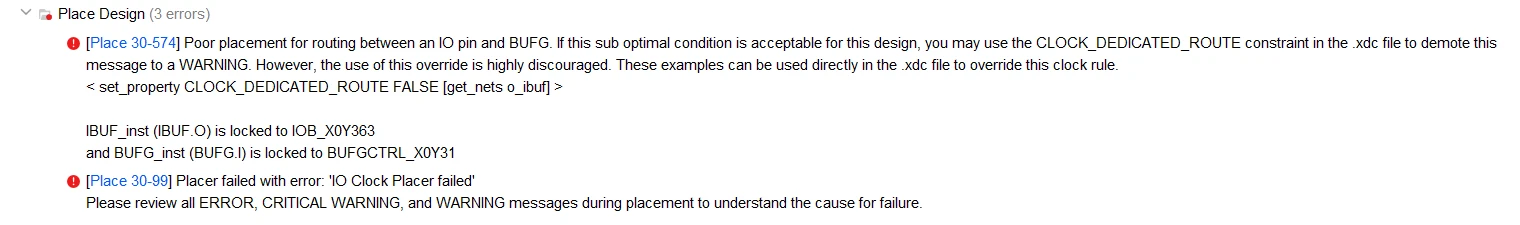

结果:Place Design中报错Place 30-574

解决:将clk端口约束到与BUFG同半区的位置

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结