您现在的位置是:首页 >学无止境 >其他类型的CMOS逻辑门网站首页学无止境

其他类型的CMOS逻辑门

简介其他类型的CMOS逻辑门

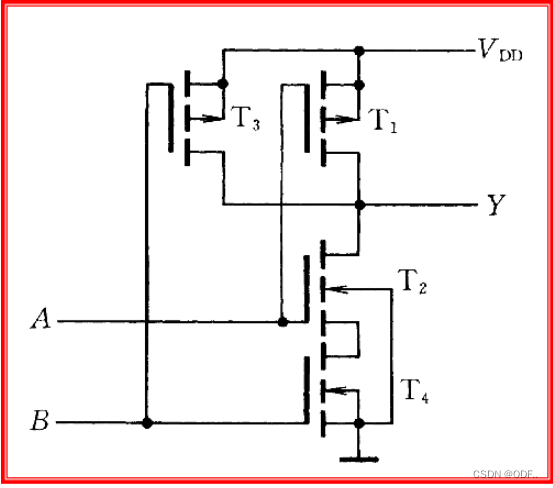

1.CMOS与非门

电路结构如图所示

![]()

如图所示,T1、 T3为两个串联的PMOS, T2、 T4为两个并联的NMOS.

A、B有一个为“0”时,T2、 T4至少有一个截止, T1、 T3至少有一个导通,故输出为高电平,Y=1.

A、B同时为“1”时,T2、 T4同时导通, T1、 T3同时截止,故输出为低电平,Y=0。

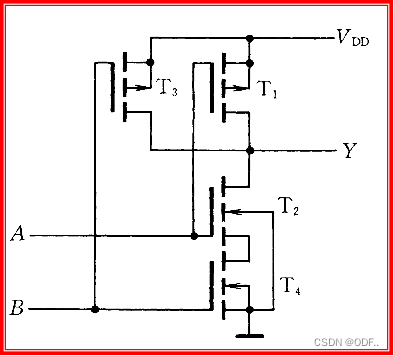

2. 或非门:

如图所示,T1、 T3为两个并联的PMOS, T2、 T4为两个串联的NMOS。

A、B有一个为“1”时,T2、 T4至少有一个导通, T1、 T3至少有一个截止,故输出为低电平,Y=0。

A、B同时为“0”时,T2、 T4同时截止, T1、 T3同时导通故输出为高电平,Y=1

3.带缓冲级的CMOS门电路

(以与非门为例)

①输出电阻RO受输入状态的影响;

②输出的高低电平受输入端数目的影响

输入端数目愈多,输出为低电平时串联的导通电阻越多,低电平VOL越高;输出为高电平时,并联电阻也多,输出高电平VOH也提高

③ 输入状态不同对电压传输特性有影响,使T2、T4达到开启电压时,输入电压vI不同

改进电路均采用带缓冲级的结构,如图为带缓冲级的CMOS与非门电路

输出为

带缓冲级的CMOS门电路其输出电阻、输出高低电平均不受输入端状态的影响,电压传输特性更陡。

口诀

箭头向外Pmos,箭头向里Nmos。

串P并N为与非,串N并P为或非。

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结