您现在的位置是:首页 >学无止境 >FM33A048B CRC网站首页学无止境

FM33A048B CRC

概述

循环冗余校验(Cyclic Redundancy Check,CRC)是最为常用的计算机和仪表数据通信的校验方法,FM33A048B中CRC计算单元为完全独立模块,通过软件控制可进行7816、I2C、UART和SPI模块有串行数据流接口的收发CRC计算和校验,也可进行Flash内容的CRC校验。

CRC算法说明

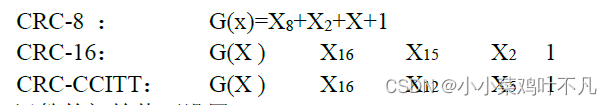

(1) CRC 模块所支持的多项式为:

(2 )CRC 运算的初始值可设置

(3 )支持输入 reflect (即将输入数据的每一 byte 依次反向后再进行计算)

支持输出 reflect (即将计算结果数据全部反向后再进行输出)

(4 )计算出的结果支持异或输出

软件配置过程

CRC 配置及计算流程如下:

1、CRC开始计算的时候,配置运算移位寄存器中的初始值,范围是0000~FFFF。

2、配置输出异或寄存器CRC_XOR

3、软件需配置好输入reflectin处理使能;输出reflectout和xorout处理使能

4、软件将需要计算CRC码的8bit数据放入数据寄存器(CRCDR[7:0]),然后自动开始计算逐次移位,总共移位8拍。(注意:触发计算的动作即是软件将需要计算CRC码的数据写入此数据寄存器,所以在这之前,所有的配置动作须完成)

5、计算完毕后,结果数据回写到数据寄存器,软件根据当前计算状态busy位来判断是否能取结果:16bit计算结果存在{CRCDR[15:0]};

6、计算完前一次CRC后,数据寄存器中会保留前一次结果,作为后续数据的移位寄存器初始值。在多次连续触发CRC计算后,软件最终读取的是累积计算的完整数据的CRC值。

DMA 接口

CRC与DMA之间通道为单向的(RAM->CRC)。CRC模块可以通过DMA模块读取并校验RAM数据,其工作流程如图所示。CRC向DMA发起请求,DMA接收请求后,读取RAM并将数据写入CRC模块的CRCDR寄存器中。CRC模块接收到数据后,撤销DMA请求并开始计算校验值,校验完成后,CRC模块重新置起DMA请求。

Flash 数据完整性校验

Flash内容的CRC校验可以在上电后进行,以保证内容正确性。CRC模块读取Flash时起始地址必须对齐word边界,每读一次flash,需要运算4次8bit CRC。软件通过寄存器指定CRC校验的起始地址和数据长度(17bit word address),起始地址寄存器兼做flash指针,CRC启动后每读取一次Flash将对指针+1,同时对长度寄存器-1,直到长度寄存器等于0,当Flash指针到达最高有效地址后,如果长度仍未减到0,指针将roll-over至0地址继续运行。

Flash校验由软件启动,启动后CRC完全占据Flash总线,CPU如果在Flash中取指将被挂起,在RAM中取指不受影响。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结