您现在的位置是:首页 >技术教程 >FPGA | 延迟模型网站首页技术教程

FPGA | 延迟模型

实际逻辑元器件和它们之间的传输路径都会存在延迟。因此,必须检查设计中的延迟是否满足实际电路的时序约束要求。可以用时序仿真的方法来检查时序(timing),即在仿真时向元件或路径中加入和实际相符的延迟信息,并进行相关计算来确定时序是否满足。

静态时序分析 (Static Timing Analysis, STA),也是一种时序验证的技术。它不关心逻辑功能的正确与否,只对设计中的时序进行计算分析,来确定电路中是否存在违反(violation) 时序约束的设计。STA 分析速度快,能够快速定位问题,但会忽略一些异步的问题。

所以 "STA + 时序仿真"是一种相对完善且安全的时序验证方法。

延迟模型

**延迟模型主要有 3 种:**分布延迟、集总延迟(lumped) 和路径延迟。

分布延迟

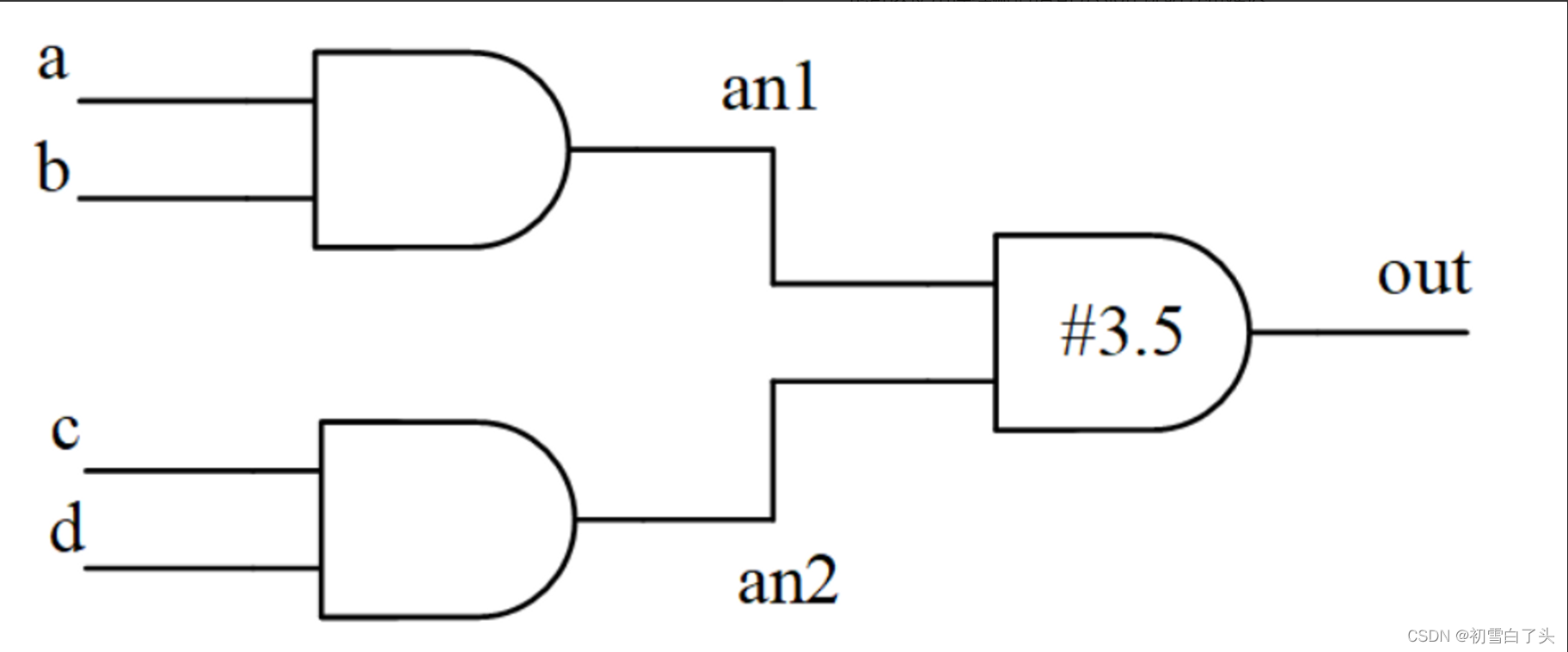

分布延迟需要给电路中每个独立的元件进行延迟定义,不同的路径有不同的延时,如下图所示。

分布延迟的 Verilog 模型和例化逻辑门单元并指定延迟值的方式基本一致。也可以使用连续赋值语句 assign 说明分布延迟。

集总延迟

集总延迟是将全部路径累计的延时集中到最后一个门单元上。

到最后一个门单元上的延迟会因路径的不同而不同,此时取最大延时作为最后一个门单元的延时。

将上述分布延迟图转化为集总延迟图,如下所示。

路径延迟

路径延迟是对每个输入引脚到每个输出引脚的所有路径指定延迟时间。

路径延迟示意图如下。

路径延迟模型需要用关键字 specify 来定义。

module and4(

output out,

input a, b, c, d);

specify

(a => out) = 2.5 ;

(b => out) = 2.5 ;

(c => out) = 3.5 ;

(d => out) = 3.5 ;

endspecify

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and (out, an1, an2);

endmodule

延迟模型比较

- 分布延迟:分布延迟将延迟时间分散在了每一个门单元上,但仍然不能描述基本单元中不同引脚上延时的差异。当设计规模变大时,结构将变的复杂。

- 集总延迟:该方式模型简单,适用于小规模的电路,但是不能描述输入端到输出端不同路径的延迟。

- 路径延迟:指定了引脚到引脚的延迟,延迟信息比较齐全。虽然信息比较多,但对于大规模电路也更容易实现。因为设计者无需关心模块内部的实现逻辑,只需要了解输入到输出引脚的延迟即可。即便模块内部逻辑有所改变,路径延迟的说明也可以保持不变。

所以,大多数逻辑门单元库中的延迟信息,都是以路径延迟的方式给出的。很多集成模块,也可以从其数据手册中直接获取到路径延迟,十分方便。

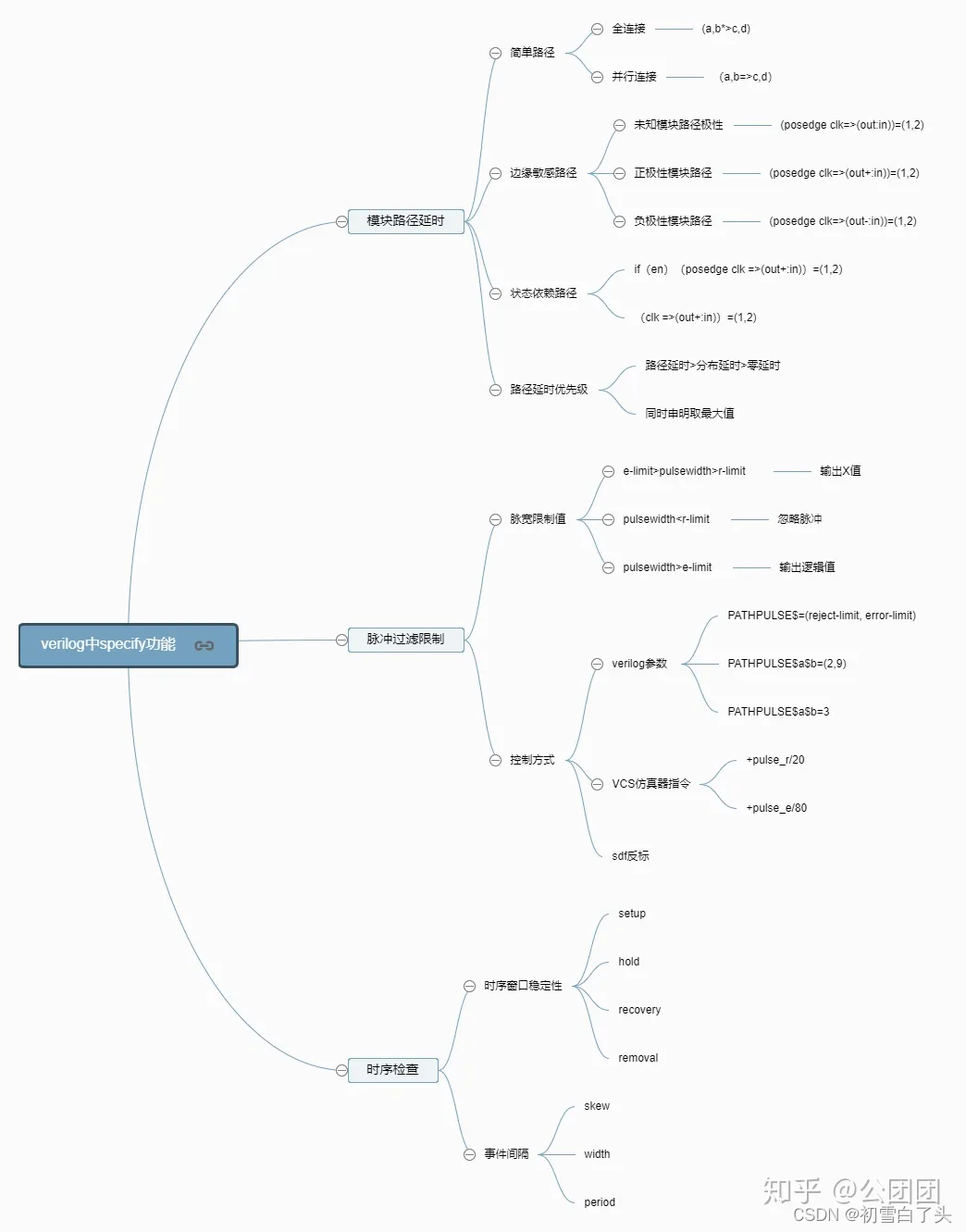

specify 块语句

路径延迟用关键字 specify 和 endspecify 描述,关键字之间组成 specify 块语句。

specify 是模块中独立的一部分,不能出现在其他语句块(initial, always 等)中。

specify 块语句主要有以下功能:

- 指定所有路径中引脚到引脚的延迟;

- 定义 specparam 常量;

- 在电路中设置时序检查。

并行连接

每条路径都有一个源引脚和目的引脚,将这些路径的延迟依次用 specify 语句描述出来,称为并行连接。

并行连接用法格式如下:

(<source_io> => <destination_io>) = <delay_value> ;

实例

module and4(

output out,

input a, b, c, d);

specify

specparam ab_2_out = 2.5 ;

specparam cd_2_out = 3.5 ;

(a => out) = ab_2_out ;

(b => out) = ab_2_out ;

(c => out) = cd_2_out ;

(d => out) = cd_2_out ;

endspecify

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and (out, an1, an2);

endmodule

可以用关键字 specparam 在 specify 块中定义延迟数值常量,然后赋值给路径延迟。

specparam 定义的常量只能在 specify 块内部使用。

并行连接中,源引脚和目的引脚是一一对应的。并行连接也支持多位宽信号间的路径延迟描述,但是位宽必须保持一致。其中,specify 块语句也可以展开描述,两种表达方式是等效的。

全连接

在全连接中,源引脚中的每一位与目标引脚的每一位相连接。

源引脚和目的引脚的连接是组合遍历的,且不要求位宽对应。

全连接用法格式如下:

(<multiple_source_io> *> <multiple_destination_io>) = <delay_value> ;

module and4(

output out,

input a, b, c, d);

specify

(a,b *> out) = 2.5 ;

(c,d *> out) = 3.5 ;

endspecify

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and (out, an1, an2);

endmodule

边沿敏感路径

边沿敏感路径用于输入到输出延迟的时序建模,并使用边缘标识符指明触发条件。如果没有指明的话,任何变化都会触发源引脚到目的引脚的延迟值的变化。

用法举例如下:

//在 clk 上升沿,从 clk 到 out 的路径上升延迟为 1,下降延迟为 2

//从 in 到 out 的数据路径是同向的,即 out = in

(posedge clk => (out +: in)) = (1,2);

//在 clk 下降沿,从 clk 到 out 的路径上升延迟为 1,下降延迟为 2

//从 in 到 out 的数据路径是反向的,即 out = ~in

(negedge clk => (out -: in)) = (1,2);

//clk 任意变化时,从 clk 到 out 的路径上升延迟为 1,下降延迟为 2

//从 in 到 out 的数据路径是不可以预知的,同向、反向或不变

(negedge clk => (out : in)) = (1,2);

条件路径

Verilog 也允许模型中根据信号值的不同,有条件的给路径延迟进行不同的赋值。

条件中的操作数可以是标量,也可以是向量,条件表达式也可以包含任意操作符。

需要注意的是,应当只使用 if 语句将条件路径中所有的输入状态都完整的声明。没有声明的路径会使用分布延迟,分布延迟也没有声明的话,将使用零延迟。如果路径延迟和分布延迟同时声明,将选择最大的延迟作为路径延迟。

但是 specify 中的 if 语句不能使用 else 结构,可以使用 ifnone 描述条件缺省时的路径延迟。

specify

if (a) (a => out) = 2.5 ;

if (~a) (a => out) = 1.5 ;

if (b & c) (b => out) = 2.5 ;

if (!(b & c)) (b => out) = 1.5 ;

if ({c, d} == 2'b01)

(c,d *> out) = 3.5 ;

ifnone (c,d *> out) = 3 ;

endspecify

门延迟路径

门延迟(上升延迟、下降延迟、关断延迟)的数值也可以通过路径延迟的方法来描述。

可以定义的延迟路径个数为 1 个,2 个,3 个,6 个, 12 个,其他数量的延迟值都是错误的。

下面举例说明门延迟模型中路径延迟的表示方法。

//1 个参数: 上升、下降、关断延迟只使用一个延迟参数

specify

specparam t_delay = 1.5 ;

(clk => q) = t_delay ;

endspecify

//2 个参数: 上升延迟(0->1, z->1, 0->z)= 1.5

// 下降延迟(1->0, z->0, 1->z)= 2

specify

specparam t_rise = 1.5, t_fall = 2 ;

(clk => q) = (t_rise, t_fall) ;

endspecify

//3 个参数: 上升延迟(0->1, z->1)= 1.5

// 下降延迟(1->0, z->0)= 2

// 关断延迟(1->z, 0->z)= 1.8

specify

specparam t_rise = 1.5, t_fall = 2, t_turnoff = 1.8 ;

(clk => q) = (t_rise, t_fall, t_turnoff);

endspecify

//6 个参数: 分别对应0->1, 1->0, 0->z, z->1, 1->z, z->0

specify

specparam t_01 = 1.5, t_10 = 2, t_0z = 1.8 ;

specparam t_z1 = 2, t_1z = 2.2, t_z0 = 2.1 ;

(clk => q) = (t_01, t_10, t_0z, t_z1, t_1z, t_z0) ;

endspecify

//12 个参数: 分别对应0->1, 1->0, 0->z, z->1, 1->z, z->0

// 0->x, x->1, 1->x, x->0, x->z, z->x

specify

specparam t_01 = 1.5, t_10 = 2, t_0z = 1.8 ;

specparam t_z1 = 2, t_1z = 2.2, t_z0 = 2.1 ;

specparam t_0x = 1.1, t_x1 = 1.2, t_1x = 2.1 ;

specparam t_x0 = 2, t_xz = 2 , t_zx = 2.1 ;

(clk => q) = (t_01, t_10, t_0z, t_z1, t_1z, t_z0,

t_0x, t_x1, t_1x, t_x0, t_xz, t_zx) ;

endspecify

//门路径延迟模型中,也可以指定最大值、最小值和典型值。

//上升、下降和关断延的延迟值:min: typical: max

specify

specparam t_rise = 1:1.5:1.8;

specparam t_fall = 1:1.8:2 ;

specparam t_turnoff = 1.1:1.2:1.3 ;

(clk => q) = (t_rise, t_fall, t_turnoff);

endspecify

X 传输延迟

如果没有指定 x 转换时间的延迟(门路径延迟中没有给出 12 个延迟参数),则规定:

- 从 x 转换为已知状态的延迟时间为,可能需要的最大延迟时间;

- 从已知状态转换为 x 的延迟时间为,可能需要的最小延迟时间。

例如,当门路径延迟中给出 6 个延迟参数时,则 x 传输延迟时间定义如下表所示:

| x 转换 | 延迟值 |

|---|---|

| 0->x | min(t_01, t_0z) |

| 1->x | min(t_10, t_1z) |

| z->x | min(t_z1, t_z0) |

| x->0 | max(t_10, t_z0) |

| x->1 | max(t_01, t_z1) |

| x->z | max(t_1z, t_0z) |

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结