您现在的位置是:首页 >技术教程 >SAR型ADC结构原理网站首页技术教程

SAR型ADC结构原理

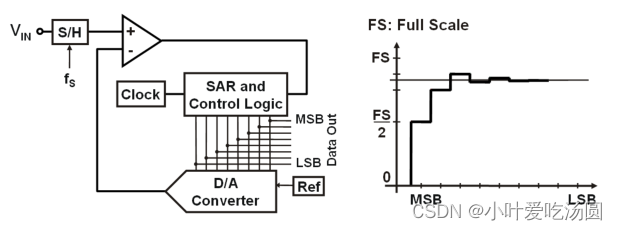

SAR型 ADC,即逐次渐进逼近型 ADC,采用的是多次比较的方式来获得最终的输出结果,具有简单易用,功耗低的特点。下图这个结构可以帮助我们容易地理解SAR型 ADC的工作过程:

如上图,假设输入信号的伪代码为 45,ADC为一个 6位的 ADC,满量程输出为 63。

1. 在采样阶段,ADC将输入信号采样至采样保持器(S/H)中并保持住,即此时 S/H中的值为 45,请记住 S/H中实际是一个模拟电压,45是我们给它定义的代表它大小的伪代码;

2. 接下来,在转换的第一个时钟上升沿,SAR寄存器首先将最高位至 1,即把 32(半个满量程),送给一个 DA转换器,DA转换器输出的模拟信号和 S/H中的模拟信号相比较,因为 45大于 32,比较器输出为高,提示 SAR的最高位应该置 1,在时钟的下降沿,ADC就将输出最高位数据(MSB)为 1;

3. 在第二个转换时钟的上升沿,SAR会将 MSB-1位置 1,此时由于 MSB已经固定为 1,SAR寄存器中的值实际为 48(32+32/2),由于 48大于 45,比较器输出为低,提示 SAR寄存器的 MSB-1位应该为 0,在时钟的下降沿,次高位的 0也被输出,同时 SAR寄存器也记住了次高位为 0的事实;

4. 依次类推,最终可以得到输出结果为:101101。

从上述过程中可以看出,SAR寄存器的位数越多,逼近得越准确,但所需的转换时间越长。

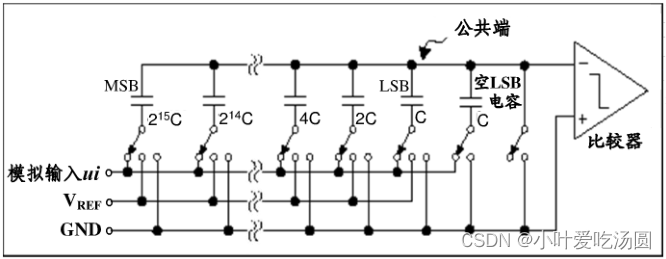

为提高 SAR型 ADC的总体转换速度,减少内部 DAC的建立时间对速度的影响,现代的SAR ADC多数采用电荷重分配的 CDAC输入结构,将采样保持与 DAC合为一体。

若 SAR型 ADC的分辨率为 n比特,则其内部由 n个按照二进制加权排列的电容和外加一个“空 LSB”电容组成的阵列,如下图所示。

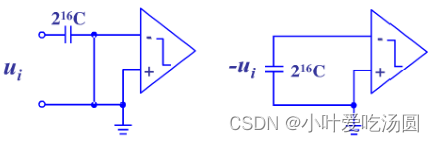

在采样阶段,电容阵列公共端,即比较器的输入端接地,自由端连接到模拟输入 ui上,使得电容阵列上的电压与 ui成正比。而在保持阶段,公共端与地断开,所有电容的自由端接地,比较器输入电压等于-ui。由此可见电容阵列起到了采样保持功能。

其转换比较方法仍然采用对分法逐次逼近。我们发现图 3-2中的电容网络从“空 LSB”电容开始,第一个 C和第二个 C并联,构成了一个 2C的等效电容,而这个等效电容又和下一个 2C电容并联,构成了 4C的等效电容,依次类推,构成了一个电容分压网络,而且每向后一级(从左向右),其电压为上一级的 1/2。其对分法比较过程如下:

1. MSB电容自由端接 Vref,其余电容自由端接地,此时公共端的电压为 1/2Vref;

2. 如果输入电压 ui大于 1/2Vref,比较器输入为-ui+1/2Vref仍然小于零,此时比较器输出为逻辑“1”;

3. 保持 MSB电容与 Vref相连,将下一个电容连接到 Vref,重复上面的判断过程,确定输出数字值;

4. 依次循环指导判定全部数字位。

从上述描述可以看出电容阵列的 SAR型 ADC好处在于减少了传统 SAR型 ADC中由于 DA引入所需的建立时间。但同时,其内部的电容值随着 ADC位数增长呈指数级增长,带来的后果是电容体积的增大,以及对芯片工艺要求的增高。这也就解释了为什么 SAR型 ADC的精度不会太高。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结