您现在的位置是:首页 >技术杂谈 >Xilinx 7系列FPGA内置ADC网站首页技术杂谈

Xilinx 7系列FPGA内置ADC

Xilinx 7系列FPGA全系内置了一个ADC,称之为XADC。这个XADC,内部是两个1mbps的ADC,可以采集模拟信号转为数字信号送给FPGA内部使用。

XADC内部可以直接获取芯片结温和FPGA的若干供电电压(7系列不包括VCCO),用于监控FPGA内部状况。同时提供了17对差分管脚,其中一对专用的模拟差分输入,16对复用的模拟差分输入,不使用的时候可以作为普通的User I/O。

01

XADC Pinout Requirements模块管脚需求:

所有的XADC模块的专用管脚都属于Bank0,所以都加上后缀_0,上图1-2表示了XADC的基本输入输出需求:上面有两种配置需求,左边使用的是Vccaux(1.8V)供电,并且使用外部的1.25V的参考源,使用外部参考源在精度和热漂移方面可以获得更好的性能,且使用一个磁珠用以隔离模拟地和数字地,以避免模拟和数字共地而把噪声带入模拟电路;右边使用的是片内的参考源,此时,VREFP脚必须按照图示连接到地。下表列出了XADC Package的管脚信息:

注:XADC模块有一专用的支持差分输入的模拟通道输入引脚(VP/VN),另外还最多有16个辅助的模拟通道输入引脚(ADxP or ADxN,x为0到15),Kintex-7不支持辅助通道6,7,13,14,15。Zynq-7000 AP SoC器件由于封装不通可能不会支持所有的辅助通道,具体要查询封装文件。

02 XADC模块的操作方式

单通道模式,在这种模式下,用户必须通过写控制寄存器40H的CH4到CH0比特来选择一个要采样的通道。另外控制寄存器40H的BU(analog input mode) 和ACQ(settling time )两个参数也必须设置。

独立ADC模式,在这种模式下, ADC A是固定用来实现一个类似于缺省模式的“监控模式”,报警输出功能是有效的,用户必须设置正确的报警门限;ADC B只能用来测量外部的模拟输入。

Single Pass 模式,在这种模式下,按用户选择的采样顺序序列顺序采样一遍后停止ADC。采样顺序序列是由用户写序列通道选择寄存器48H和49H 来设定的。

Continuous Sequence 连续序列模式,这种模式和Single Pass 模式很相似,区别是采样完一遍后系统自动重新开始序列采样,故为连续采样。

模式选择是由控制寄存器41H 的SEQ3到SEQ0比特决定,具体如下图示:

03 IP核设置

Basic 设置

关于XADC具体的结构,功能和各个参数的含义,需要注意的是:

1.关于参考电压的设置,会影响误差范围及采样值的计算公式。

2.模拟差分输入对模拟信号幅值有要求,需要外边模拟电路进行一定程度的转换。

假设现在需要用XADC来获取几个模拟信号的信息,那么应该如何操作呢。下面解释一种设置方式。

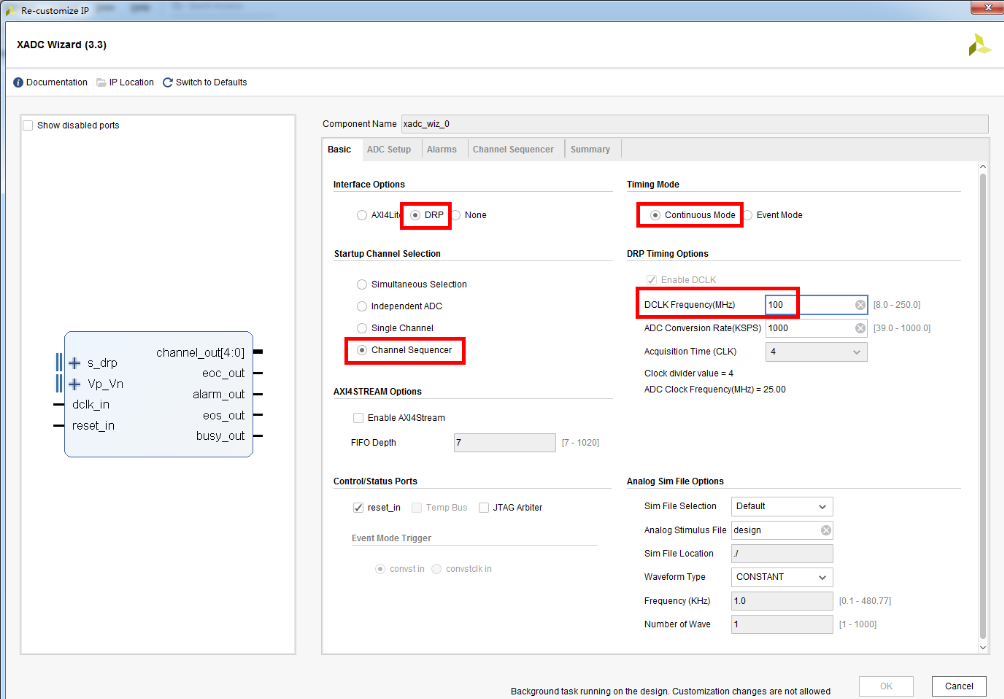

注意红框中的几点:

1.使用DRP端口获取数字信号,这样控制似乎更简单一些。

2.使用连续采样模式,ADC一直工作在数据采集模式,采集后就可以进行输出。

3.使用Channel Sequencer模式,由于只有两个XADC而需要采样的数据过多,所以让XADC依次陆续进行采样。

4.设置好DRP端口的时钟频率,50或100M都可以,无特殊要求。

ADC Setup 设置

IP设置第二页,主要是设置Calibration、平均值和外部MUX。这几个可以暂时跳过,等熟悉XADC的使用后在进行深入了解。

Alarms 设置

第三页设置告警参数,可以不用。如果需要的话,可以设置一下,便于使用。

channel 设置

第四页设置需要使用的通道,这里选择温度和三个供电电压,并选择一个专用的模拟输入通道和前三个复用的模拟输入通道。

最后一页是Summary,可以看看设置是否有问题,没有需要设置的地方。

这个时候最基本的一个多通道获取数据的XADC设置好了,至于设置中没有细说的地方,可以等熟练使用之后进行研究,找出最合适的使用模式。

04

Port 例化

下面是如何使用这个生成的IP。由于使用DRP端口来读取数据,所以需要设计一个DRP读写控制器。不过由于XADC本身就提供了一些信号,所以这个设计其实非常简单。

余下四个DRP端口,两个输出两个输入。两个输出直接引出来,其中do_out就是最终需要的数据。这个端口是16bit,取高12bit即可(对应XADC中宣称的12位)。

XADC的IP端口中还有两个,名为eoc_out和channel_out。将eoc_out连接到DRP端口的den_in端口,含义是当多路采样的某一路完成采样后,则启动DRP端口操作,开始进行读取数据。将channel_out补两位之后送入daddr_in作为DRP端口操作的地址信号。这样就完成了DRP的读写操作。

不过这样输出的数据,会周期性的在几个端口数据之间变化。所以通常在后端加一个过滤设置,具体行为是,当代表DRP操作完成的drdy_out拉高的时候,根据channel_out的值来判断是哪一个通道的。

关于每个采样通道的具体地址,可以参考手册:

温度换算公式和曲线如下图所示:

电压换算公式和变化曲线如下图所示:

至于模拟差分输入Pin,直接送到顶层的相对应管脚即可。注意Vivado工具可能需要对复用的模拟Pin进行电平约束,根据VCCO的电压值选择相应的lvcmos即可,例如1.8V的VCCO就选择lvcmos18即可。

这样就可以获取对应的模拟采样数据了。由于绝大部分情况下需要检测的模拟信号变化相对较慢,使用XADC是足够用于检测的。

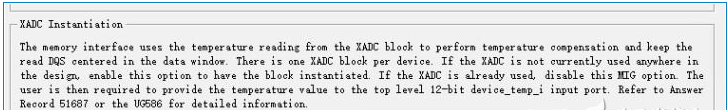

涉及到XADC的使用问题还有MIG IP。MIG是Memory Interface的IP,也就是DDR3之类的DDR存储器IP。由于此类接口一般速率过高,会需要温度信息对接口做一定的矫正。在MIG IP的配置中,会默认启动XADC。

此时的XADC仅仅需要提供温度信息就可以了。当需要提供更多信息,就需要独立配置XADC,这样工程中就会生成两个XADC;或者例化了两个MIG IP,这样各自就会需要一个XADC。由于硬件中只有一个XADC模块,当发现工程中需要多个XADC模块的时候,工具就会提示出错。

解决方案也非常简单,MIG IP中去掉XADC。然后在设计中独立例化XADC IP。根据上文的做法获取温度信息后送往MIG。MIG IP去掉XADC后会生成一个温度端口用来接收数据。这样就不会发生冲突。

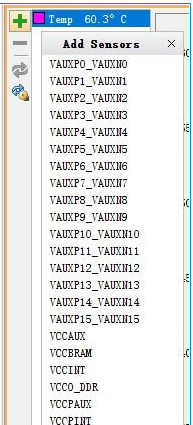

另外一个非常便捷的获取温度信息的方案就是使用Hardware Manager。在Hardware Manager中打开XADC就能看到温度信息。

其实XADC所有通道数据都可以通过这个方法获取。

可以看到上图界面温度信息Temp 60.3℃。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结