您现在的位置是:首页 >技术杂谈 >如何减少电路中传导噪声网站首页技术杂谈

如何减少电路中传导噪声

从传导噪声的起源,可以看出可以通过减少器件噪声或周围环境的干扰来降低传导噪声对电路的影响。但在某些场合我们需要特定的器件,同时要求在特定场景下工作。举个例子:在电气隔离系统中,我们需要对电源进行隔离,而 DC/DC转换器会产生很大的开关噪声。在实际操作时,我们一般从以下三个方面来减少电路中的传导噪声的影响。

(1)使用旁路电容减少电源线上的传导噪声

无论电路的供电形式如何,在电源处始终用上旁路电容,否则电源噪声会对电路的性能产生影响。一般在电路设计中旁路电容用在两个地方:一个是电源供电处,另一个在所有有源器件,无论是模拟器件还是数字器件的供电引脚处。具体采用的旁路电容值取决于所选用的器件。如果器件的带宽小于或等于 1MHz,0.1μ F的电容可以很好地滤除噪声;当器件的带宽大于 10MHz时,选用 0.01μ F的电容则比较合适;处于两者之间两个大小的电容均可。

此外,对于特定芯片,最佳的选择是参考芯片数据手册决定旁路电容的大小取值。同时,可以通过下面所述的方法来进行合适容值的选择。

如上图所示,右图展示了不同容值的陶瓷电容的相应曲线。横轴为频率,纵轴为电容表现出来的阻抗。我们可以看到 0.1μ f的电容大约在 2MHz时其阻抗表现低于 1Ω ,即对2MHz左右的信号滤波效果最好;同理,0.01μ f的电容则对对 10MHz左右的信号滤波效果最好。结合左图的 ADC的电源电压抑制比在不同频率段的表现,以及干扰噪声的频率,可以选择最合适大小的电容。

在放置旁路电容时注意应尽可能靠近器件供电引脚,走线应尽可能短。同时,如果选用了两个旁路电容,容值较小的应更靠近芯片引脚。

(2)合理的 PCB设计减少地平面上的传导噪声

实际上对地以及电源层的设计和实现对低噪声设计来说是至关重要的。一般来说,所有的电路设计中对地的处理应当是铺铜处理。在带有模拟器件或者混合器件的电路中,没有铺地层是非常不明智的。首先,模拟信号是以地为基准的,地噪声问题会给电路带来更大的影响;其次,地平面的优点在于在宽频域上都处于低阻抗状态,现代数字器件的开关频率都在MHz以上,当数字器件工作时会有大量的高频电流返回到地层;如果没有地平面,而采用地线的方式连接所有地,细长的地线所带有的寄生电感会在高频信号的冲击下产生大量电压噪声,或常说的地弹;再次,合理规划地平面上的电流路径,绝对避免将数字地或功率地上的电流流入模拟地;最后,尽量保持地平面的完整性,分割的地线会导致电流回流路径紊乱,因此要避免走线跨越分割的地平面。在电源层设计上,同样的,在成本允许的条件下尽可能的采用电源平面,同时在高频大功率走线上(如开关电源的功率回路)注意用覆铜的方式确保线宽,尽可能减小电源走线上的寄生电感。

(3)在 ADC前使用低通滤波器减小信号链中的传导噪声

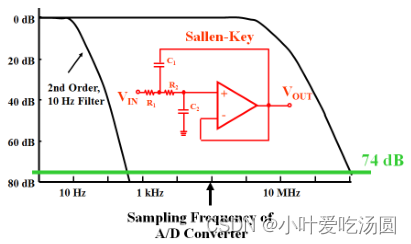

除却在电路中添加旁路电容之外,在送入 ADC之前的信号需首先进行滤波处理。在 ADC前添加的低通滤波器主要目的在于滤除送入 ADC信号中的高频成分。一方面是避免混叠,另一方面是为了减少进入 ADC的宽带噪声,前面我们提到过电阻的热噪声,运放的白噪声都是和带宽相关的指标,如下图,在添加二阶低通滤波器之前,以 12位 ADC的信噪比 74dB(12×6.02+1.76=74dB)为阈值,所选放大器构成的信号链的带宽超过 30MHz,这意味着所有 30MHz内的宽带白噪声被积分后都会影响到ADC的性能,而在我们添加一个 10Hz的二阶低通滤波器后,只有 1KHz以内的噪声才会对ADC造成影响。 由此可见低通滤波器的巨大 作用:

总结下来,减少传导噪声的方法有:

(1)替换噪声系数较大的器件

(2)在电源引脚旁添加去耦电容

(3)改善信号线走线并铺地

(4)进入 ADC之前,对信号链路进行滤波

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结