您现在的位置是:首页 >技术教程 >基于DSP+FPGA+ADS1282支持32Bit高精度数据采集方案(二)模拟电路设计网站首页技术教程

基于DSP+FPGA+ADS1282支持32Bit高精度数据采集方案(二)模拟电路设计

简介基于DSP+FPGA+ADS1282支持32Bit高精度数据采集方案(二)模拟电路设计

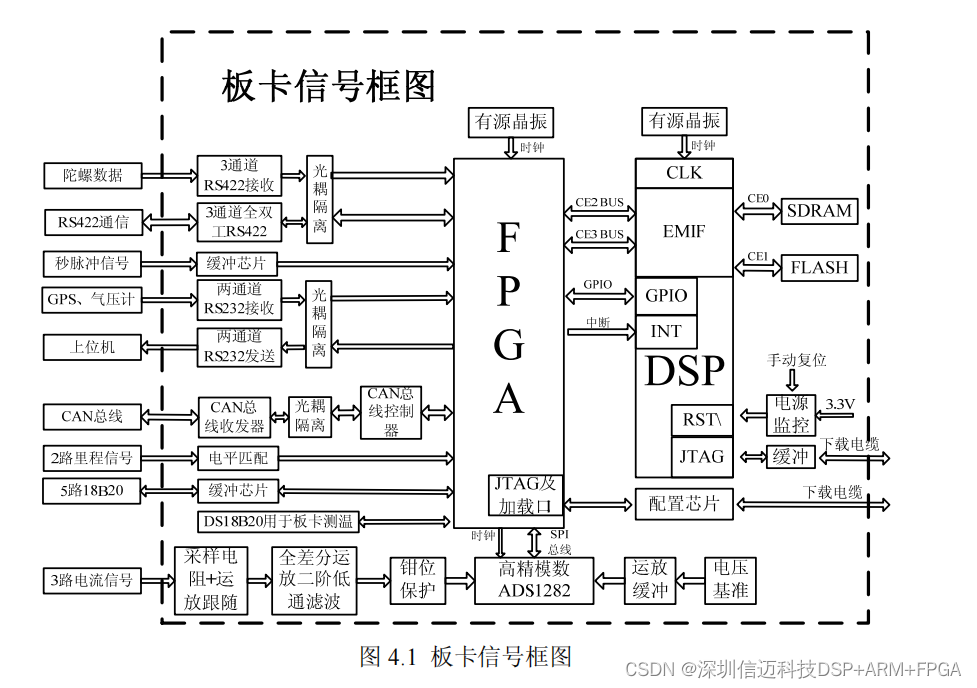

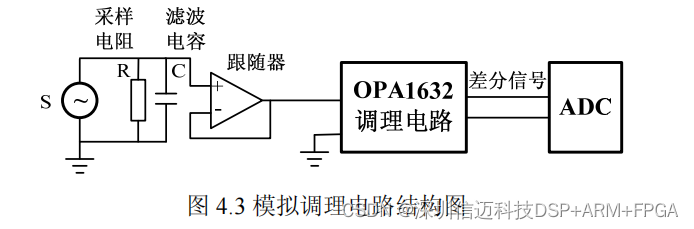

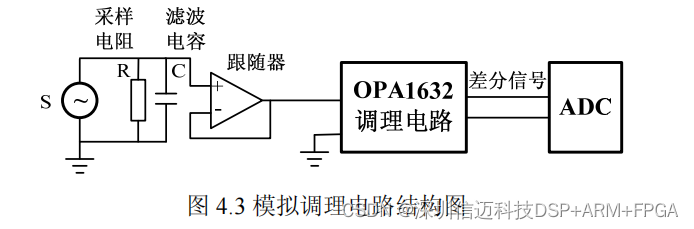

如图

4.1

所示是系统硬件系统的信号框图,数字信号处理板上的主要核心是

两个处理芯片,即

FPGA

和

DSP

,其中

FPGA

主要作用是做

DSP

和外围接口的

桥梁及数据预处理,

DSP

做为数据解算核心。

FPGA

通过各种的数据总线接收外部设备传输过来的数据,并进行打包处理

以及其他预处理,再把数据存放在指定的内建存储器上。

DSP

通过

EMIF

总线接

口读取相应的数据,并作做数据解算处理。处理过程中的参数及处理的结果由

DSP

通过

EMIF

总线接口写入

FPGA

内指定的存储器内,并由

FPGA

通过

CAN

总线

接口发送出去。

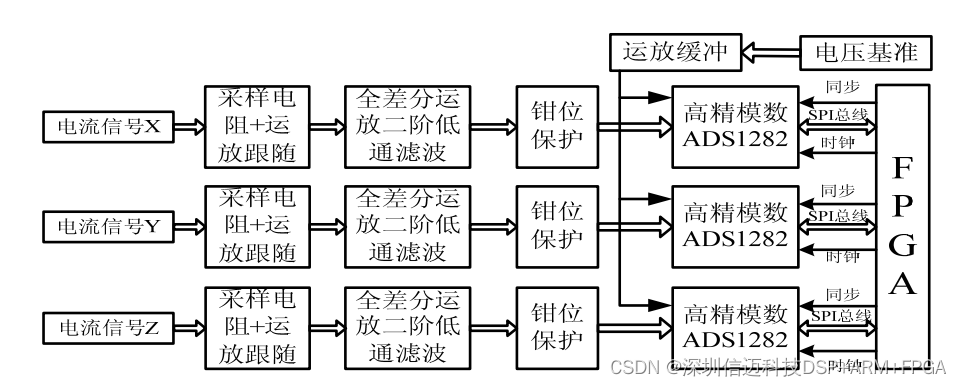

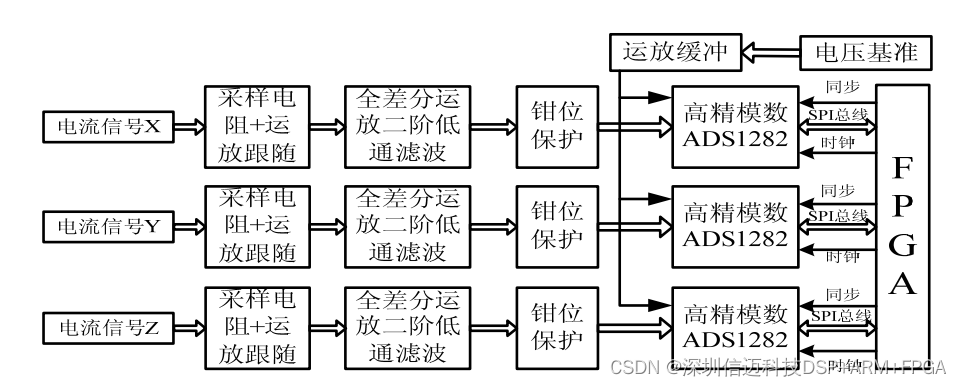

4.2

高精度数据采集电路设计

本系统数据采集模块的设计结构框图如图

4.2

所示。由于需要采集的是传感

器输出来的电流信号,而

ADC

要求输入是电压信号,所以输入的电流信号需要

转换为一个与电流成正比的电压信号。本设计中采用一个高精度低温漂的采样电

阻来实现这一功能。所得到的电压信号输入给一个二阶低通滤波器,该低通滤波

器由一个全差分运算放大器构成,在此起到滤去高频噪声的功能。其输出经过箝

位保护后,直接输入到高精度的模数转换器的差分输入端。箝位保护由箝位二极

管构成,用于保护

ADS1282

的输入信号瞬时超载。当输入信号电平超出内部

ESD

二极管的额定值时该箝位二极管可对输入进行钳位,实现电平保护的功能。模数

转换器的数字通信接口直接接至

FPGA

,由

FPGA

构建的

SPI

总线来读取转换得

到的数据。

4.2.1

模拟信号调理电路设计

1

、电流采样

由于加速度计信号对精度的要求很高,因此前级处理电路结构和器件选择很

重要。运算放大器需选用高共模抑制比、高精度、低漂移和低噪声的器件;低通

滤波器需具有良好的线性与截止频率,并且模拟前端要求是差分信号输入。

如图

4.3

所示,输入的电流信号经过一个采样电阻后得到与之成正比的电压

信号,因此采样电阻的性能直接影响所得的电压信号的稳定性和精度。选用

VISHAY

公司生产的

VSMP

系列超精密金属箔电阻,它具有极好的负载寿命稳定

性和接近于零的温漂,且具有极低的噪声和极高的阻值精度。滤波电容

C

可以一

定程度上滤除高频信号的干扰。由采样电阻得到的电压信号经过跟随运放缓冲后

再输入调理电路。该跟随缓冲运放选用

OPA227

,该芯片同样具有极低的噪声

(3 nv / z

H

),宽的通频带(

8

MHz

),很高的共模抑制比(

CMMR

,

138

dB

),高

的开环增益(

160

dB

),低的输出偏置电压(

75

uVmax

),极低的温度漂移(

0.1

uV/

℃

)

和宽的电源电压(

±2.5

V

~

±18

V

)等特性。工作温度范围为

-55

~

+125

℃

[28]

。

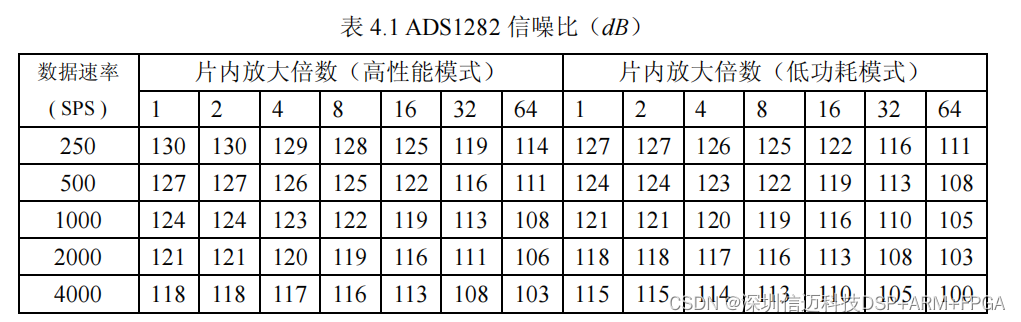

2

、调理电路

ADS1282 的输入是采用差分电压输入形式,差分输入最明显的优势在于其抗

干扰能力强,并能有效抑制自身对外界的电磁干扰。因为当外界存在噪声干扰时,

会几乎同时被耦合到两条信号线上,再经两信号差值后,外界干扰信号几乎完全

被抵消。此外,两根信号线对外辐射的电磁场也可以相互抵消。除此之外,它的

时序定位精确高。由于差分信号的开关变化位于两个信号的交点,因而受工艺、

温度影响小,能降低时序上的误差。

由于模数转换器的输入端是差分形式,而信号源却是单端的。因此,需要设

计一个低噪声的模拟信号调理电路来接口。单端转差分电路一般来说有两种方法,

一是用多个运算放大器构成一个调理电路;二是使用单片的全差分运放芯片。第

一种方法使用的器件较多,不可避免的引入了更多的噪声,而第二种方法结构简

单,所用的分立器件很少。因此本设计选取一片全差分运算放大器作为前级模拟

信号调理及滤波功能电路,所选的全差分运算放大器为

OPA1632

。

OPA1632

是一款高性能和低噪声的全差分运算放大器。失真低至

0.000022%

,

噪声低至

1.3nV

/

Hz

[29]

。采样电阻输出的电压经过电容滤波后输入到

OPA1632

。

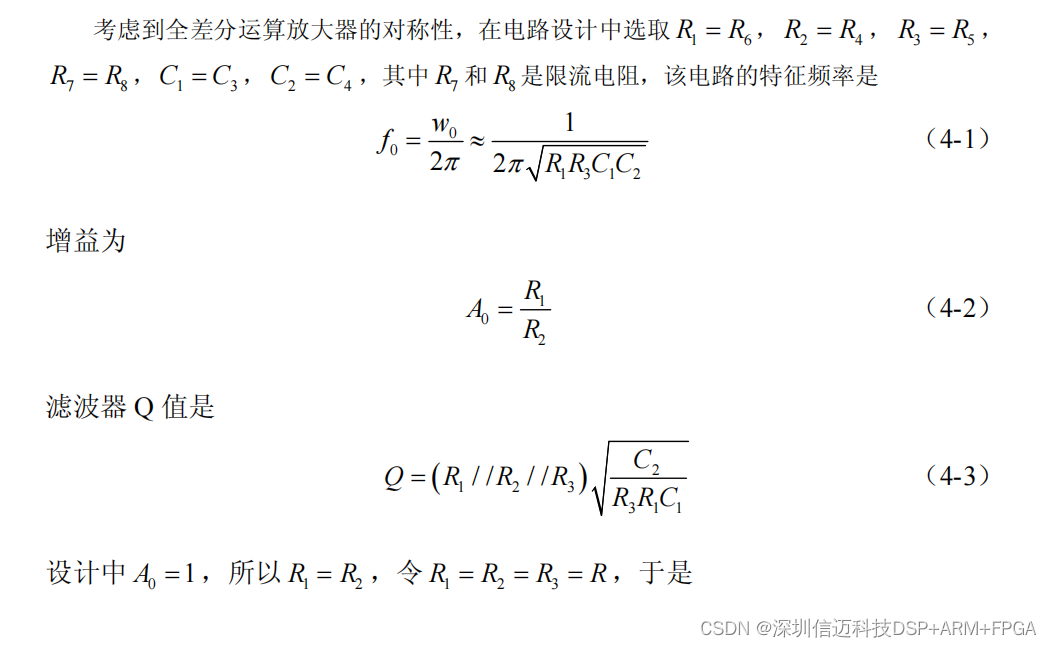

如图

4.4

所示,

OPA1632

设计成二阶巴特沃斯低通滤波器,通频带宽根据设计要

求通过选取不同的电阻电容来实现。巴特沃斯滤波器的特点是通频带内的频率响

应曲线最大限度平坦,没有起伏,而在阻频带则逐渐下降为零。

如图

4.5

所示,是该低通滤波器的

Multisim

仿真波特图。由图可知,该滤波器

性能良好,在频带内增益曲线非常平坦,没有起伏,通带外增益衰减很快。

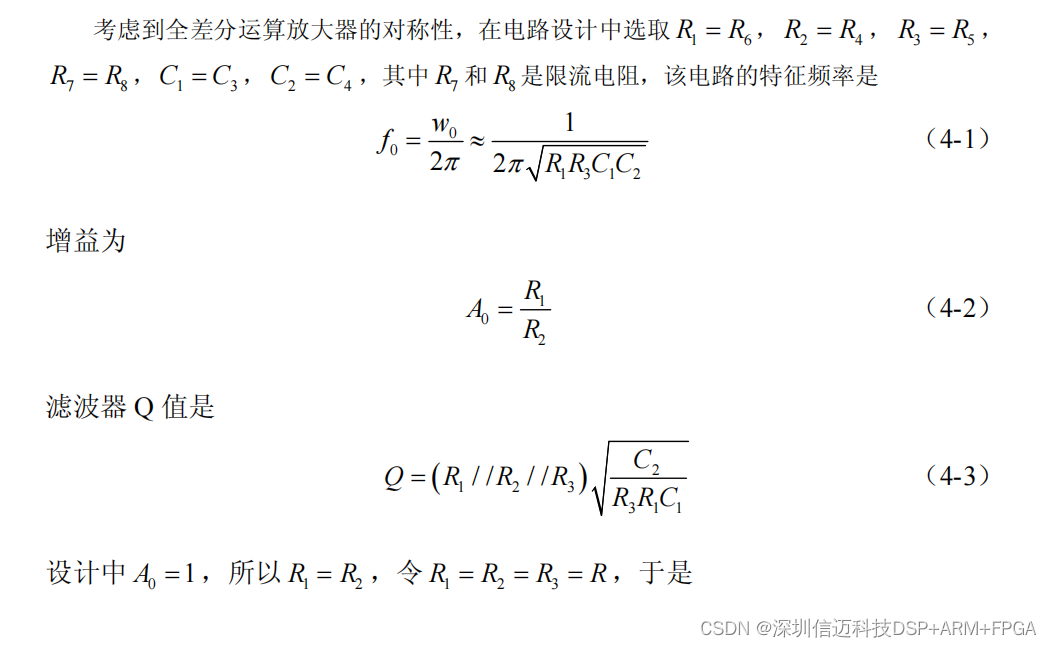

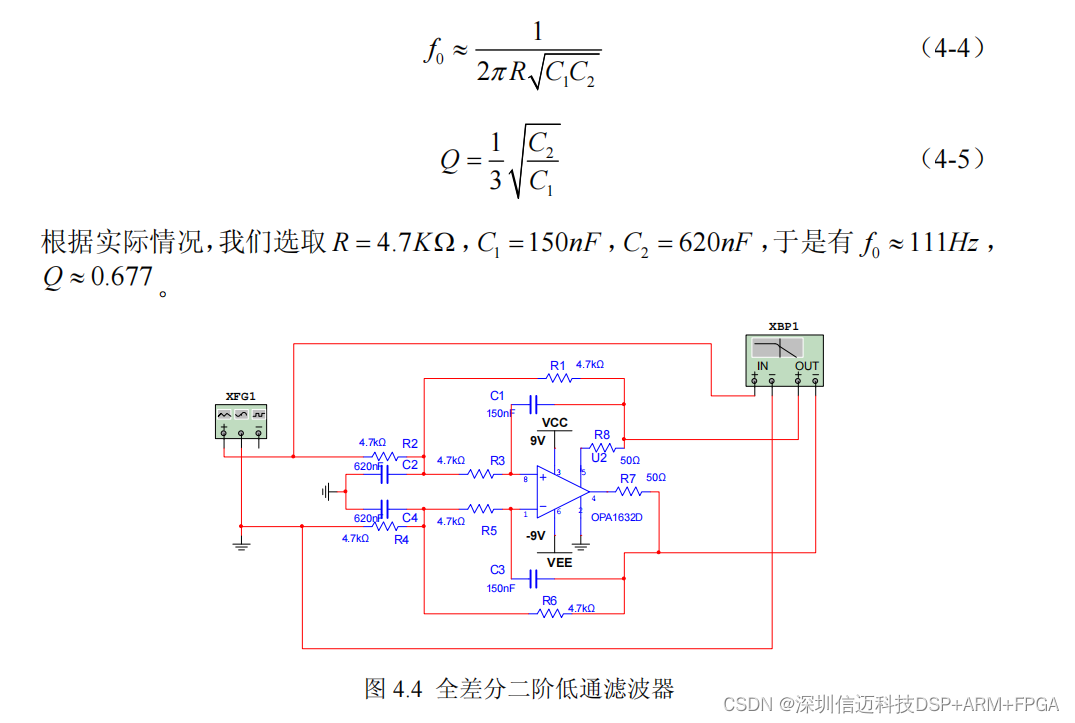

4.2.2

ADC

电路设计

ADS1282

的工作模式主要有低功耗模式和高性能模式两种,其可以通过寄存

器的设置来选择。在不同的模式,不同的速率以及不同的片上可编程方法大器

(

PGA

)的放大倍数下,其有不一样的信噪比,如表

3.1

所示。由该表可知,同

样条件下,高性能模式比低功耗模式信噪比高。此外,速率越低,

PGA

放大倍数

越小,信噪比越好。

根据设计要求,我们选择高性能模式中的

500SPS

速率模式,该模式下信噪

比为

127

dB

。根据公式(

2-9

),可以计算出此时

ADC

的有效位(

ENOB

)为 20.8位,符合并超出本设计的技术要求。

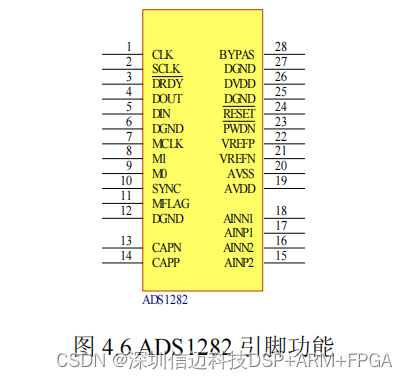

ADS1282 采用 28 引脚贴片 TSOP 封装,引脚功能如图 4.6 所示。

CLK

:主时钟输入;

SCLK

:串行时钟输入;

DRDY

:数据准备好输出,在其下降沿读出数据:

DOUT

、

DIN

:串行数据输出、输入

MCLK

、

M1

、

M0

:若工作在调制器模式,

MCLK

为调制器时钟输出,

M1

、

MO

为调制器的数据输出,否则这些引脚不使用,需接固定值。

SYNC

:同步输入,用于实现多芯片同步工作;

MFLAG

:超量程标志,

0

表示正常,

1

表示超量程;

DGND

:数字地,该引脚是接地点的核心;

CAPN

、

CA-PP

:内部

PGA

输出端,在

CAPP

与

CAPN

之间需连接一只

10 nF

的

电容;

AINP2

、

AINN2

,

AINP1

、

AINN1

:正、负模拟输入端;

AVDD

、

AVSS

:正、负模拟供电电源,单极性(

+5

V

)或双极性(

±2.5

V

);

VREFN

、

VREFP

:正、负基准输入;

PWDN

:掉电输入,低电平有效;

RESET

:复位输入,低电平有效;

DVDD

:数字供电电源:

+1.8

V

~

+3.3

V

;

BYPAS

:校准输出:与

DGND

之间接

1

μ

F

电容。

1

、

ADC

内部结构及其工作原理

ADS1282

的内部结构如图

4.7

所示,主要由多路选择器(

MUX

)、可编程增

益放大器(

PGA

)、

4

阶△

-∑

调制器、可编程数字滤波器、超量程检测电路、增

益和失调校准模块、控制器及

SPI

串行总线接口等组成

[27]

。

多路选择器

MUX

允许的

5

种设置包括,通道

1

输入、通道

2

输入、输入通道

1

、

2

同名端之间短路、内部

400

Ω

短路测试及共模测试。多路选择器后面是差分

输入和差分输出的可编程增益放大器(

PGA

),该

PGA

的增益范围是

1

~

64

,可

通过

CONFIG1

寄存器中的

PGA[2:0]

设置。

PGA

通过

300

Ω

的内部电阻差分驱动后

级的调制器,在引脚

CAPP

与

CAPN

之间需接

COG

型陶瓷电容

C

作为抗混叠滤波器,

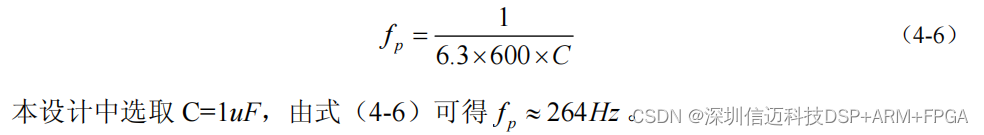

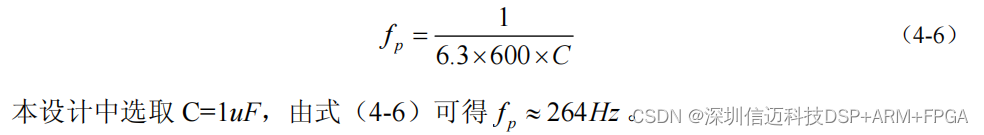

用于滤除调制器采样时产生的瞬间干扰,其转折频率为

ADS1282

的调制器是一个高性能和固有稳定的四阶

∑-

△调制器,该调制器把

量化噪声转移到有效频带之外的更高频带上,数字滤波器可以对噪声进行有效地

滤除,从而可降低量化噪声的影响。调制器差分输入信号

VIN

(其中

VIN=(AINP-AINN)

×

PGA

)的范围是

VREF

(

VREF=VREFP-VREFN

),即

±2.5

V

。

当调制器的输入超出满量程范围时,调制器将进入稳定的饱和状态,这时数字输

出代码可能是正满量程值或者负满量程值,而在

MFLAG

引脚就会由低电平变成

高电平,因此可通过检测该引脚的电平来判断输入是否超量程。调制器采样频率

在高性能模式下为

CLK/4=1.024

MHz

,在低功耗模式下为

LCK/8=512

KHz

,其中

CLK

是主时钟电路中为

4.096

MHz

。

调制器的数据流输出可被直接访问,也可连接到片内的数字滤波器上从总线

上提供可读的输出转换编码。通过设置

CONFIGO

寄存器的位

FILTR[1

:

0]=00

,

可使调制器工作在输出模式。这时,引脚

MO

和

M1

变成调制器的数据输出,MCLK

为调制器的时钟输出。但若调制器不工作在输出模式时,这些引脚为输入引脚,

且需接固定电平。

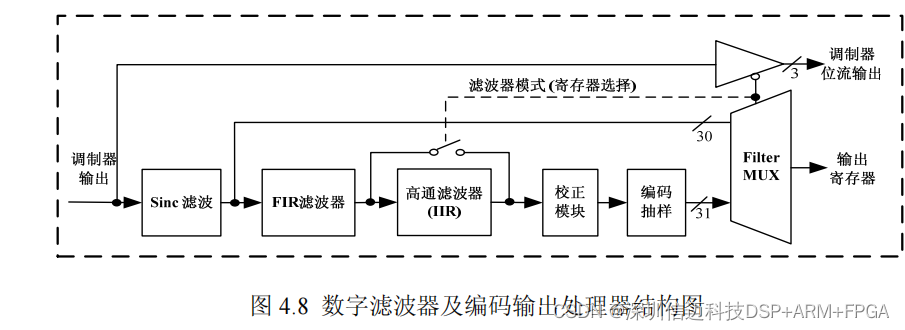

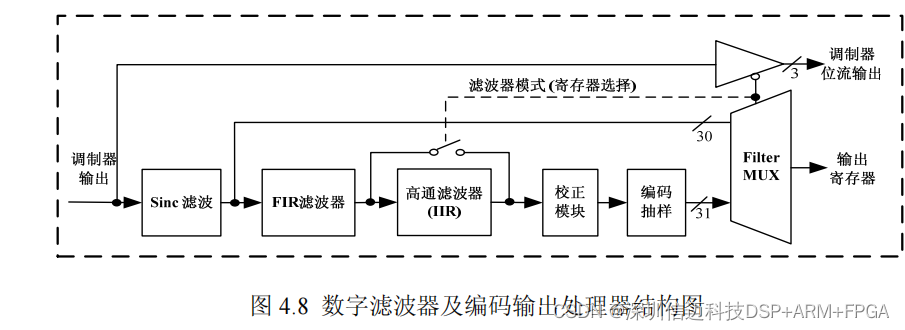

如图

4.8

所示,数字滤波器接收调制器输出的数据流并对其进行抽取。数字

滤波器由

3

个级联的滤波器组成。即一个抽取率可调的五级

sinc

滤波器、

1

个具

有可编程相位

32

倍率抽取的有限冲击响应(

FIR

)低通滤波器和一个可编程的一

阶高通滤波器(

HPF

)。数据可从这

3

级滤波器模块的任意一级输出,若完全不使

用片上滤波器,则可选择调制器直接输出;若部分使用片上滤波器,则可选择

sinc

滤波器输出。本设计中使用

sinc

滤波器以及

FIR

低通滤波器,采用

500SPS

速率

的滤波器配置。

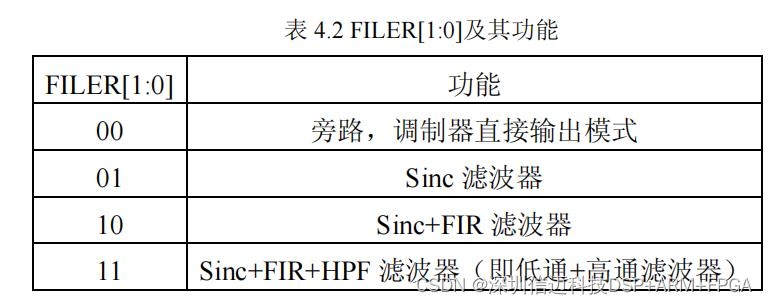

数字滤波器的选择是由 FILER[1:0]位来决定,如表 4.2 所示。

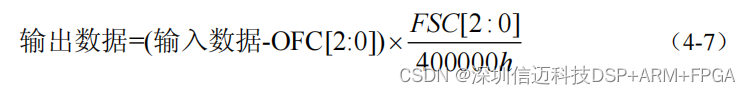

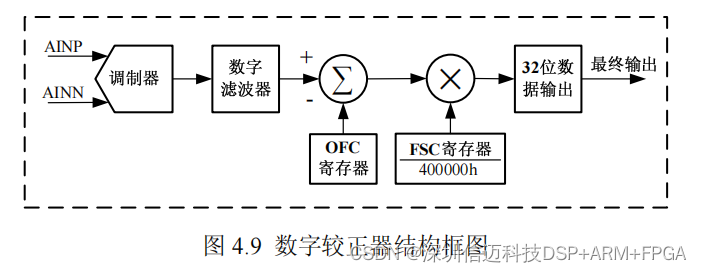

如图

4.9

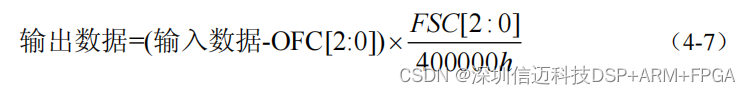

所示,在片内滤波器后面,还带有强大的数字校正处理模块,由一

个加法器和一个乘法器组成,最终的数字输出可由公式(

4-7

)表示

通过配置寄存器 OFC 和 FSC 就可以对原始数据进行偏移量和增益的校正处理。

2

、

ADC

数据输出接口电路

ADS1282

是通过串行接口(

SPI

)来输出数据和访问寄存器。

ADS1282

以二

进制补码的格式输出

32

位宽的转换数据,其中最高位和最低位是符号位,

‘0’

表

示正数,

‘1’

表示负数。

SPI

接口包括

SCLK

、

DIN

及

DOUT

三路基本信号。数据

在

SCLK

的上升沿移入

DIN

,在

SCLK

的下降沿移出

DOUT

。

DRDY

是输出信号,

当其是低电平时,表示新的转换数据已准备好可以被读出了。

FPGA

判断该引脚

的电平,来读取数据。若

SCLK

保持为低电平达

64

个

DRDY

周期,则数据传输

或命令输入将终止,且

SPI

接口复位。下一个

SCLK

脉冲将启动一个新的通信周

期。当

SCLK

无效时需保持低电平。图

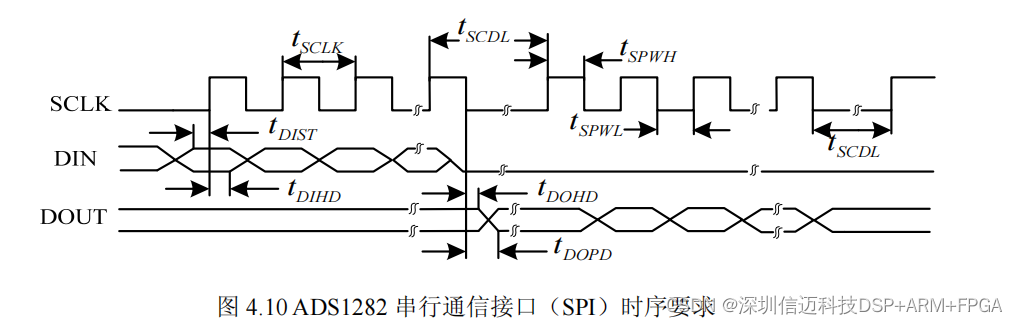

4.10

是串行接口

SPI

的时序要求。

(

1

)

t

SCLK

:

SCLK

周期,最小为

2

个

1

f

sclk

,最大为

16

个

1

f

sclk

;

(2) :

SCLK

时钟宽度,最小为

0.8

个

,

t

SPWH L

1

f

sclk

,最大为

10

个

1

f

sclk

;

(3)

t

DIST

:

DIN

建立时间,最小为

50

ns

;

(4)

t

DIHD

:

DIN

保持时间,最小为

50

ns

;

(5)

t

DOPD

:

SCLK

下降沿到一个新的

DOUT

输出的延时,最大为

100

ns

;

(6)

t

DOHD

:

SCLK

下降沿到

DOUT

开始输出的保持时间,最小为

0

ns

;

(7)

t

SCD

命令的最后一个时钟的上升沿到读写寄存器的第一个时钟的上升

沿的时间间隔,最小为 24 个

L

: 1 f

sclk

;

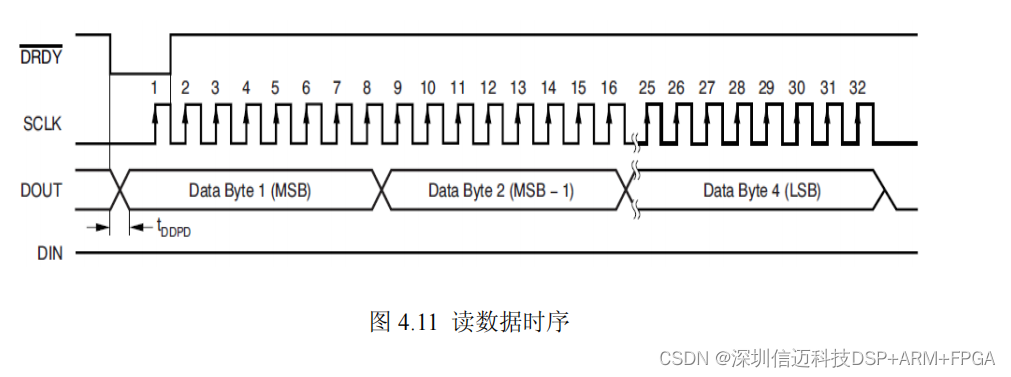

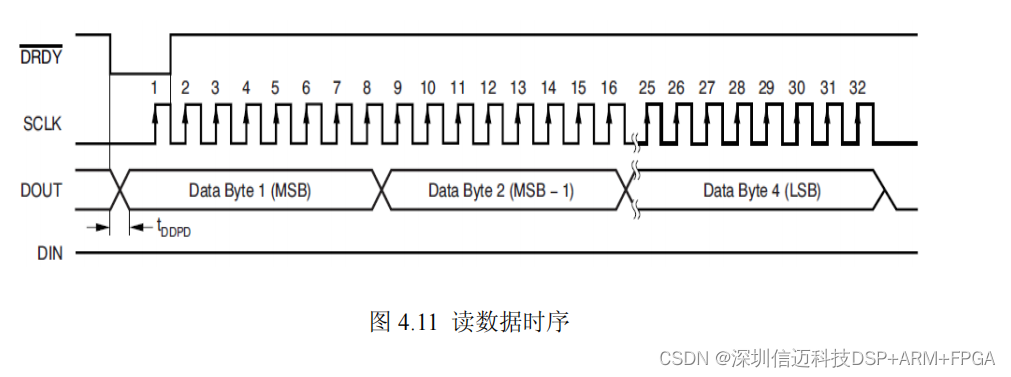

4.11

给出的是串行接口

SPI

的读数据时序,一个数据包由

4

个

8

位的字节

组成,高位在前,低位在后,由

DOUT

引脚串行输出。

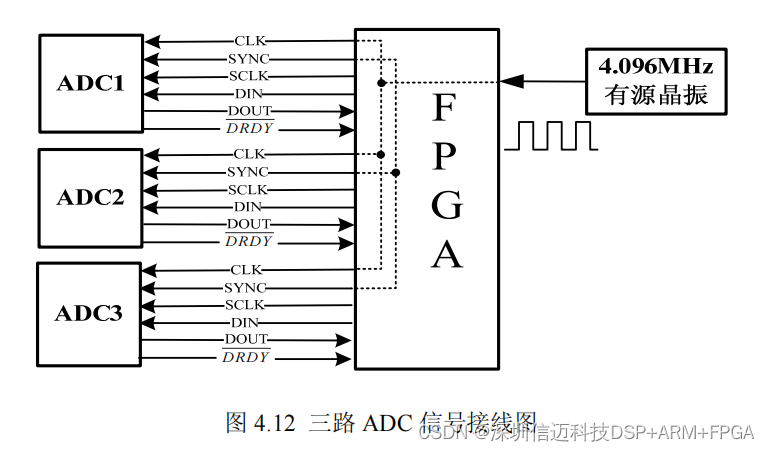

本系统中的三路

ADC

要求同步工作,以防止不同步造成的误差。

ADS1282

的同步功能可以由引脚

SYNC

来控制,也可以通过发送同步命令来实现。当同步

发生时,

ADC

复位内部存储器,并开始新的转换。同时

ADS1282

有单次脉冲同

步和连续同步两种同步模式。

(

1

)单次脉冲同步模式。这种模式下

ADC

在工作中只需要同步一次。同步

发生在

SYNC

上升沿后的下一个

CLK

信号的上升沿之后,或者同步命令后的第

8

个

SCLK

时钟上升沿。同步后

ADC

就不需再次同步,不断地按照选定的速率进

行转换。

(2)连续同步模式。这种模式下

ADC

在工作中需要不断地同步,每同步一

次进行一次转换,同步发生在每个

SYNC

的上升沿后。

本设计采用

SYNC

引脚同步单次脉冲同步方式。三路

ADC

通过

SYNC

引脚

同步后,按照相同的转换速率不断地进行模数转换。三路

ADC

的接线示意图如

图

4.12

所示,每个

ADC

的通信接口有主时钟

CLK

、同步信号

SYNC

、串行总线

时钟

SCLK

、串行数据

DIN

及

DOUT

和数据准备好信号

DRDY

。其中主时钟

CLK

和同步信号

SYNC

,在

FPGA

内部是同一个信号,这样就可以得到比较严格的同

步。

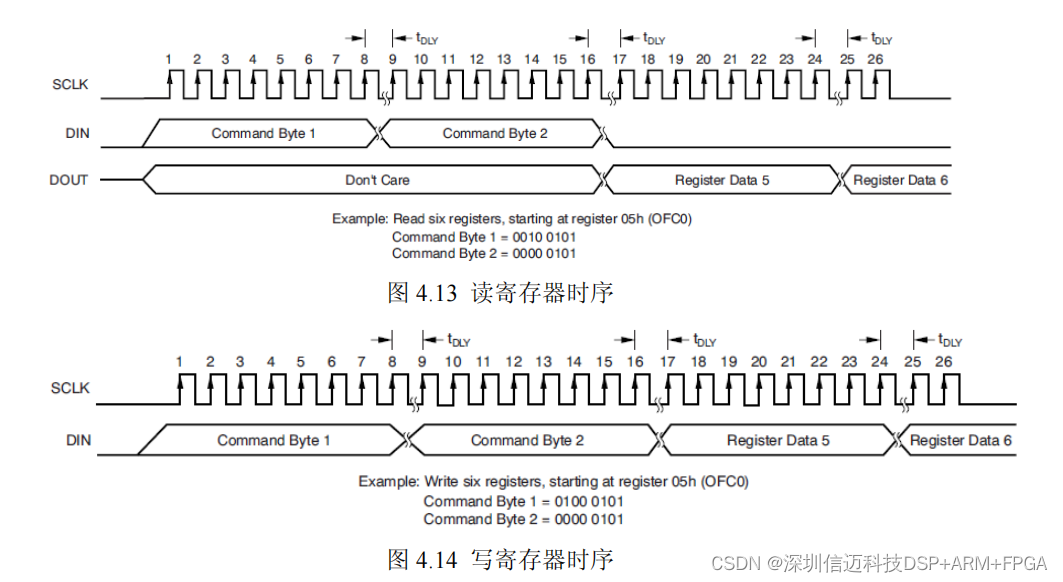

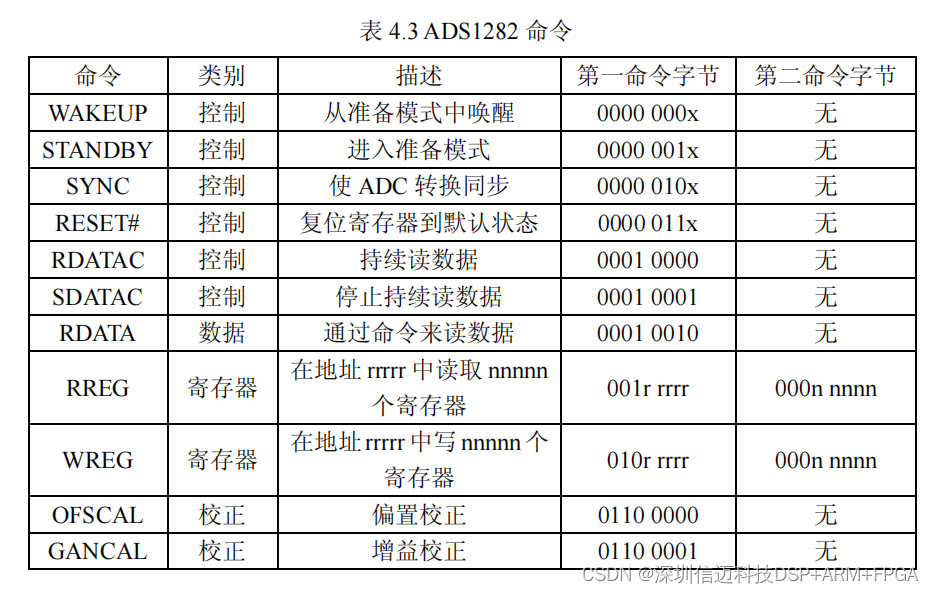

是通过向

ADS1282

发送命令来实现对其进行控制,包括对寄存器的读写操作

等。图

4.13

和图

4.14

分别给出了读写

ADC

寄存器的时序图。在读写寄存器时要

先发送命令字,然后再对相应寄存器进行读写操作。在命令字中包含了寄存器的

起始地址和要写多少个寄存器等相关信息,如表

4.3

所示

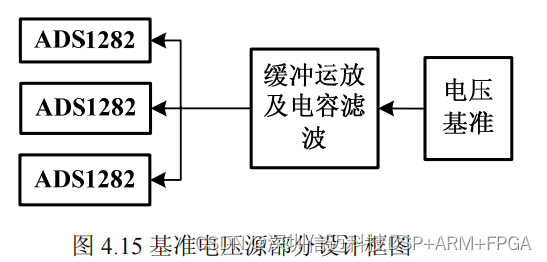

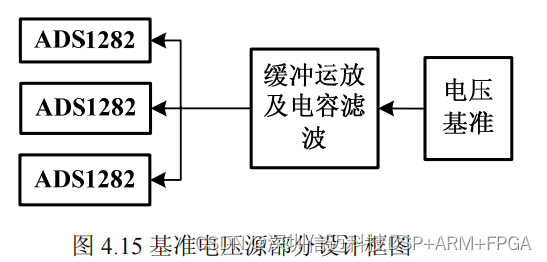

4.2.3

基准电压源设计

ADC

转换系统的精度直接依赖于其电压基准的精度,电压基准产生一个精确

的输出电压值,用于确定

ADC

的满量程输入电压值。因此,基准电压源的好坏

直接影响到

ADC

的性能。在整个工作温度范围内,基准电压的任何误差都会严

重影响

ADC

的线性度和无杂散动态范围(

SFDR

)。精密外部电压基准比片内带

隙电压基准具有更低的温度系数、热迟滞和长期漂移性,因此本设计中采用外部

基准电压源。

该电路原理框图如图

4.15 所示,基准电压源芯片输出的电压信号经过一级运

算放大器缓冲及电容滤波后,直接输入到三片

ADC

的基准输入接口。缓冲运放

可以进一步滤除电路的噪声和提高基准负载的电压调整率。

经过比较和筛选,本设计中选用美国模拟器件(

AD

)公司的基准电压源芯片

ADR445B

来提供基准电压,其输出电压为

+5

V

。该芯片具有极低的噪声(

0.1

Hz

~

10

Hz

下为

2.25

uVpp

),极低的温票(

1

ppm/

℃

),宽的工作温度范围(

-40

~

+125

℃

),

等特点

[30]

。 缓冲运放选用 OPA227

,其同样是具有极低的噪声(3 nv / z

H

),宽的通频 带(8MHz

),高的共模抑制比(

CMMR

,

138

dB

),高的开环增益(

160

dB

),低的 输出偏置电压(75

uVmax

),宽的电源电压范围(

±2.5

V

~

±18

V

)等特性。工作温

度范围为

-55

~

+125

℃

,也满足技术要求。

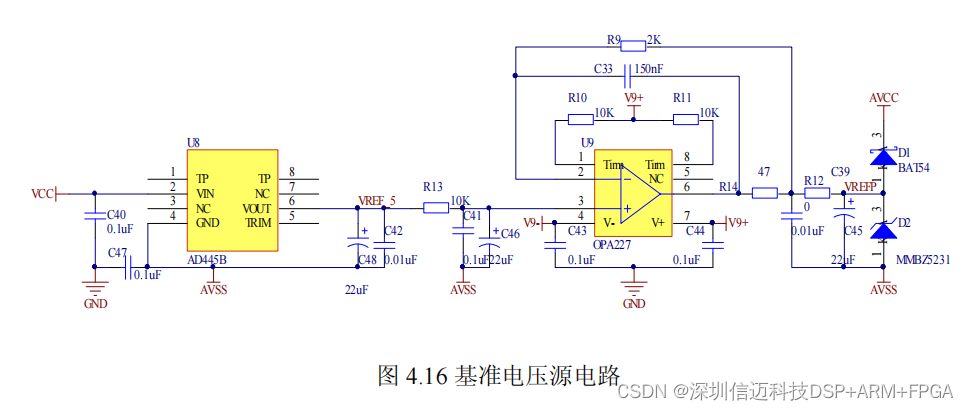

基准电压源电路设计如图

4.16

所示,基准电压源芯片输出的

5

伏电压经过阻

容滤波后输入到运算放大器中。该运放设计为跟随器,可以增强基准电压的输出

电流和提高输出负载率,以减少因负载变化而产生的纹波噪声。图中的

R10

和

R11

是用于调整运算放大器的零位偏移。

D1

和

D2

对运放输出的电压进行钳位,

用于保护

ADC

。

信迈提供模拟电路设计+DSP+FPGA研发生产一体化方案。

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结