您现在的位置是:首页 >其他 >ASIC-WORLD Verilog(9)循环语句网站首页其他

ASIC-WORLD Verilog(9)循环语句

写在前面

在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。

这是网站原文:Verilog Tutorial

这是系列导航:Verilog教程系列文章导航

Verilog语法中有四种基本的循环语句,他们都只能在always和initial块中使用:

- foever

- repeat

- while

- for

这些语句基本都和C语言中的对应语句类似,如果你学过C语言(或者其他变成语言),那么对这4中语句的用法都不会陌生。

foever语句

forever是一个无限执行的语句,它不会停止。它的一般语法是这样的:

syntax : forever < statement >

forever的无限循环特性使得其一般被用来生成时钟信号:

module forever_example ();

reg clk;

initial begin

#1 clk = 0;

forever begin

#5 clk = !clk;

end

end

initial begin

$monitor ("Time = %d clk = %b",$time, clk);

#100 $finish;

end

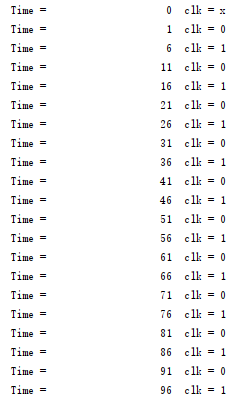

endmodule这是仿真的结果,生成了时钟信号(注意这里用了$finish来结束仿真,不然这将会无限循环):

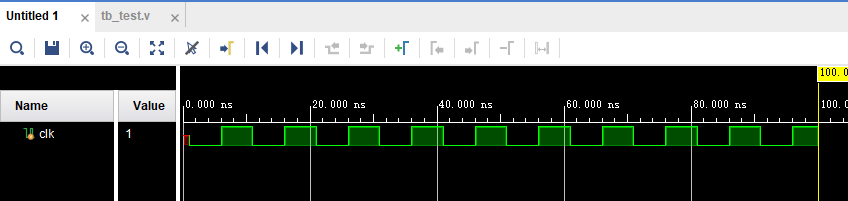

或者看看更直观的波形图:

repeat语句

repeat语句不会无限循环,它只会执行特定的次数,这个特定次数将在repeat后面由开发者指定。这是它的一般语法:

syntax : repeat (< number >) < statement > //< number >内指定循环次数

下面的例子,实现了8次向左移位,即repeat(8)次。

module repeat_example();

reg [3:0] opcode;

reg [15:0] data;

reg temp;

always @ (opcode or data)

begin

if (opcode == 10) begin

// Perform rotate

repeat (8) begin

#1 temp = data[15];

data = data << 1;

data[0] = temp;

end

end

end

// Simple test code

initial begin

$display (" TEMP DATA");

$monitor (" %b %b ",temp, data);

#1 data = 18'hF0;

#1 opcode = 10;

#10 opcode = 0;

#1 $finish;

end

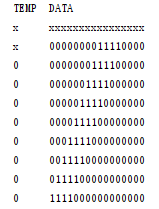

endmodule这是仿真结果:

while语句

和C语言的while语句类似,Verilog中的while语句也是当其表达式为真时,即执行对应的语句;反之亦然。它的一般语法:

syntax : while (< expression >) < statement >

下面的例子,实现当data是不同的值时,对loc分别赋值。

module while_example();

reg [5:0] loc;

reg [7:0] data;

always @ (data or loc)

begin

loc = 0;

// If Data is 0, then loc is 32 (invalid value)

if (data == 0) begin

loc = 32;

end else begin

while (data[0] == 0) begin

loc = loc + 1;

data = data >> 1;

end

end

$display ("DATA = %b LOCATION = %d",data,loc);

end

initial begin

#1 data = 8'b11;

#1 data = 8'b100;

#1 data = 8'b1000;

#1 data = 8'b1000_0000;

#1 data = 8'b0;

#1 $finish;

end

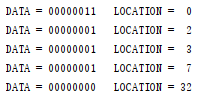

endmodule这是仿真结果:

for语句

和其他变成语言中的for语句一样:

- < initial assignment >只会在循环开始时执行一次

- 当表达式< expression >为真就会一直执行循环内对应的语句

- 在每次循环结束时执行 <step assignment>

这是它的一般语法:

syntax : for (< initial assignment >; < expression >, < step assignment >) < statement >

需要注意的是,由于Verilog没有 ++或者--这个运算符,所以在for语句中请不要写这种类似的语句:

i++;

i--;

而是要写成这样:

i = i + 1;

i = i - 1;

下面的例子通过for循环来个一个深度为8的RAM赋值:

module for_example();

integer i;

reg [7:0] ram [0:7];

initial begin

for (i = 0; i < 8; i = i + 1) begin

#1 $display(" Address = %g Data = %h",i,ram[i]);

ram[i] <= i; // Initialize the RAM with 0

#1 $display(" Address = %g Data = %h",i,ram[i]);

end

#1 $finish;

end

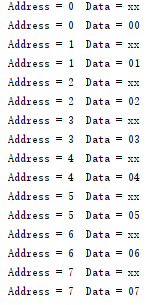

endmodule仿真结果如下,分别打印出了赋值前后的RAM中的数据值。

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结