您现在的位置是:首页 >学无止境 >AHU QuartusII 5.0 多功能时钟设计网站首页学无止境

AHU QuartusII 5.0 多功能时钟设计

文章目录

前言

摘 要

《可编程逻辑系统综合设计》是基于《数字逻辑》这门专业课,旨在培养学生对中规模逻辑器件的使用和使用Quartus II 5.0仿真软件的能力。从时钟的发展历史出发,它经历了机械表到电子表再到晶体管,再到现在的数字时钟等几个阶段。现代时钟的功能已经十分完善,在人类的正常生活生产中离不开时钟,因此本学期,学生将在老师的指导下完成多功能时钟的设计,使用的基本器件包括但不限于,74193,74194计数器,7485比较器,D触发器等。多功能时钟的功能包括,时钟正常走时,设置时钟时间(即通过按键设置不同的时间,用于日常生产生活中的时间校准),设置闹铃(通过不同的按键来设置闹铃,用于日常生产生活的时间提醒),设置时间时对应7段数码管闪烁(便于使用者知晓设置时间时对应的7段数码管),使用蜂鸣器播放音乐(增强多功能时钟的生活性)。

关键词:可编程逻辑系统综合设计,多功能时钟

1.概述

电子时钟主要是利用电子技术将时钟电子化、数字化,拥有时钟精确、体积小、界面友好、可扩展性能强等特点,被广泛应用于生活和工作当中。

本多功能时钟设计主要为实现一款可正常显示时钟,可设置时钟时间,可设置闹铃,在设置时间的时候对应7段数码管闪烁提示用户设置,在闹铃响起时可以利用蜂鸣器播放《晴天》前奏的功能。

本文对当前电子时钟开发手段进行了比较和分析,最终确定了采用QuartusII 5.0仿真软件,运用74138译码器,74193,74194计数器,7485比较器,D触发器等中规模逻辑器件完成多功能时钟的设计。

2.多功能时钟课程设计任务及要求

2.1设计任务

了解可编程阵列逻辑的概念

掌握QuartusII5.0软件的使用方法

掌握中大规模数字系统设计方法

2.2设计要求

设计一个有时,分,秒的电子钟,实现如下功能:

实现时钟正常走时

可以设置时钟分秒

添加设置闹铃功能

添加设置时间时7段数码管闪烁功能

添加播放音乐的功能(晴天前奏)

3. 多功能时钟详细设计

3.1多功能时钟设计的总体思路(流程)

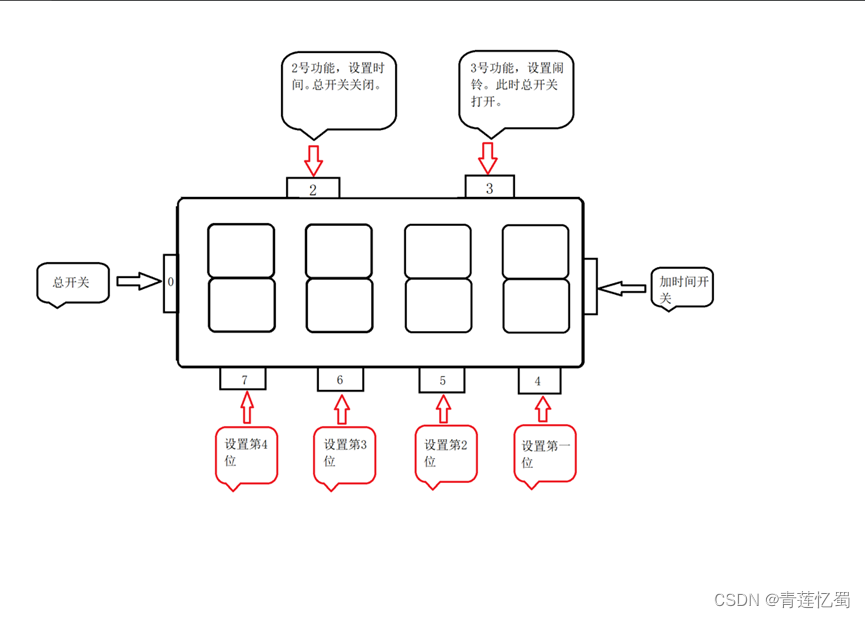

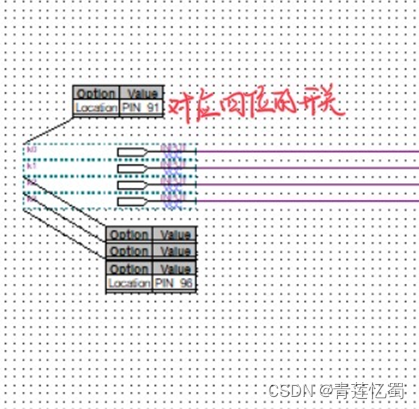

首先我们确定需要几个功能按键,第一,走时开关,当打开走时开关时,多功能时钟开始正常走时,当关闭走时开关时,多功能时钟停止走时。第二,设置时间开关,当用户想要设置时间时,首先需要将走时开关关闭,然后打开设置时间开关,开始设置时间。第三,设置闹铃开关,当用户想要设置闹铃时,时间正常走时,此时走时开关为打开状态。第四,选择开关,当用户想要设置时间或者闹铃时,需要选择设置哪一个7段数码管,我们称之为A(最低位)、B(次低位)、C(次高位)、D(最高位)。第五,增加开关,用户通过按动增加开关来增加7段数码管的值。第六,设置开关,此开关我们区别于增加开关,给用户提供便利,无需持续手动按动增加开关,只需在四个设置开关上按动对应10进制数字的8421BCD码即可(例如我要将A设置为7,只需按动0111)。其中在所有的功能里,闪烁和音乐不具备外部接口,在多功能时钟内部实现。

3.2 时钟走时模块

3.2.1 功能

多功能时钟正常走时

3.2.2 设计思路和过程

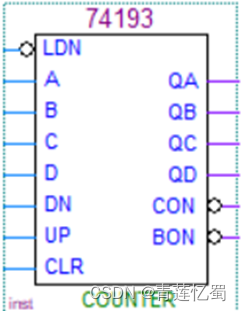

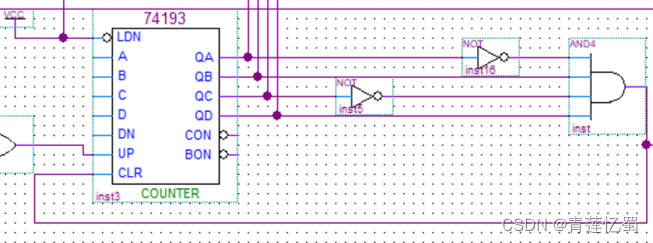

利用74193计数器实现基本的累加计数的功能

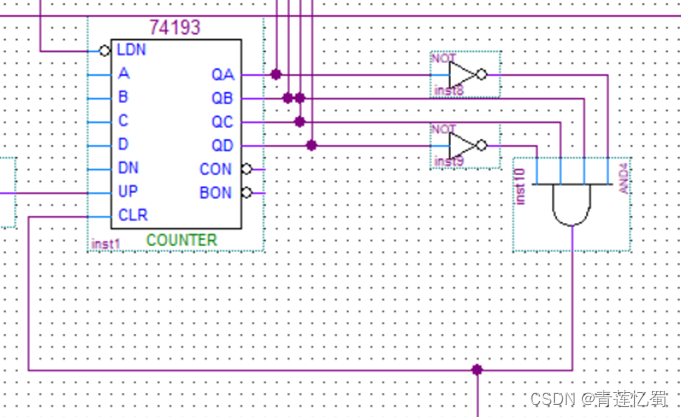

由于电子表存在十进制和六进制,需要对计数器的输出做出模十和模六的处理

十进制计数器

六进制计数器

当前一位的值达到进位条件时,会传递一个高电平到该位的CLR,将该位清零,同时传递一个高电平到下一位的UP,使下一位加一,以完成时钟的基本走时功能。

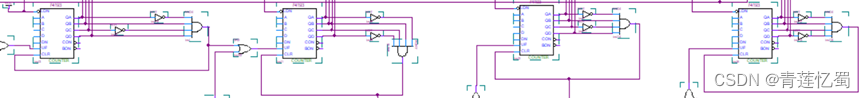

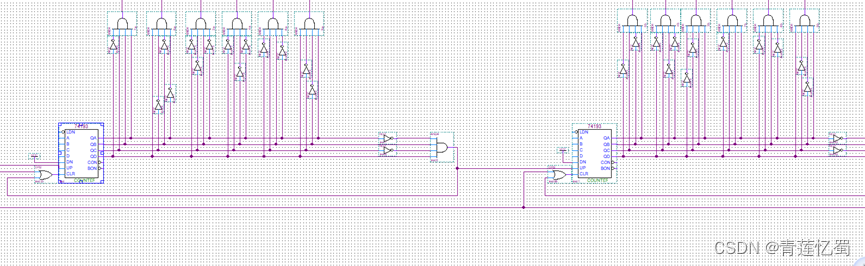

3.2.3 电路图

3.3 设置时间模块

3.3.1功能

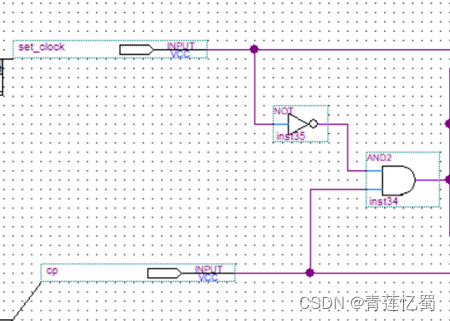

使用手动脉冲信号,通过74193计数器的CPu接口在原显示位上对该位数字进行修改,从而实现对时钟的时间预置

3.3.2 设计思路和过程

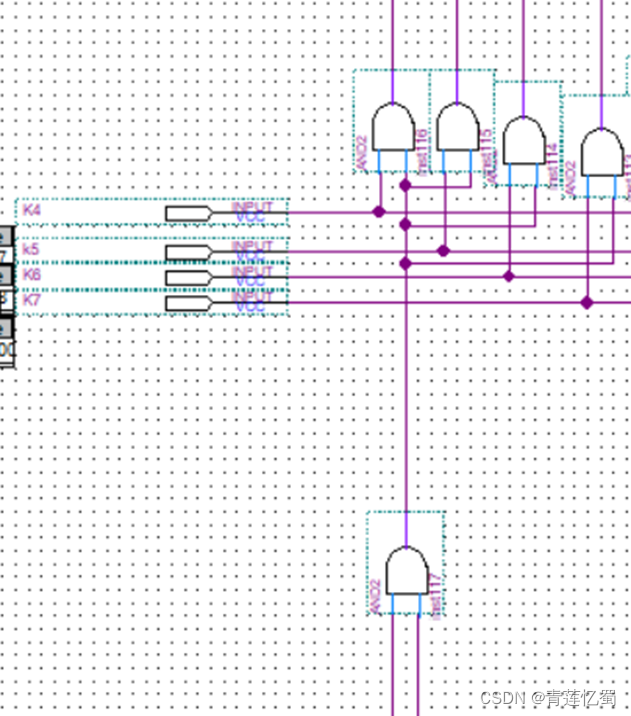

通过设置四个开关选择来实现对相应位数的设置

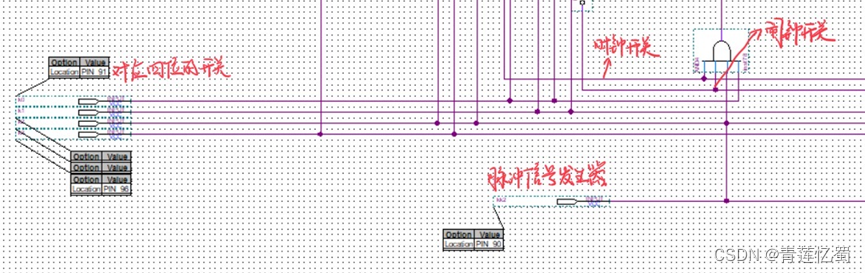

3.3.3电路图

当时钟开关关闭时,CP信号无法通过与门传向 CPu,此时脉冲信号可以通过与门传向CPu,完成手动设置时间;相反,当时钟开关打开时,时钟只能通过CP信号累加,脉冲信号无法通过与门干扰时钟正常走时。

3.4 设置闹铃模块

3.4.1功能

添加设置闹铃功能

3.4.2 设计思路和过程

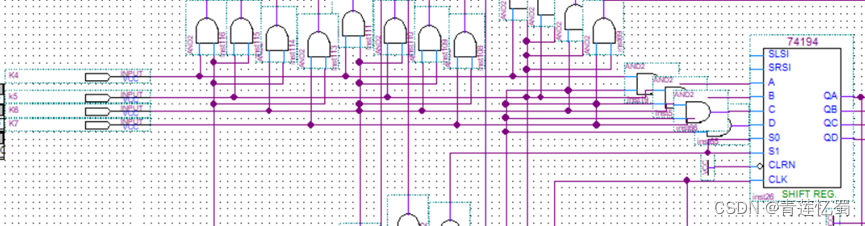

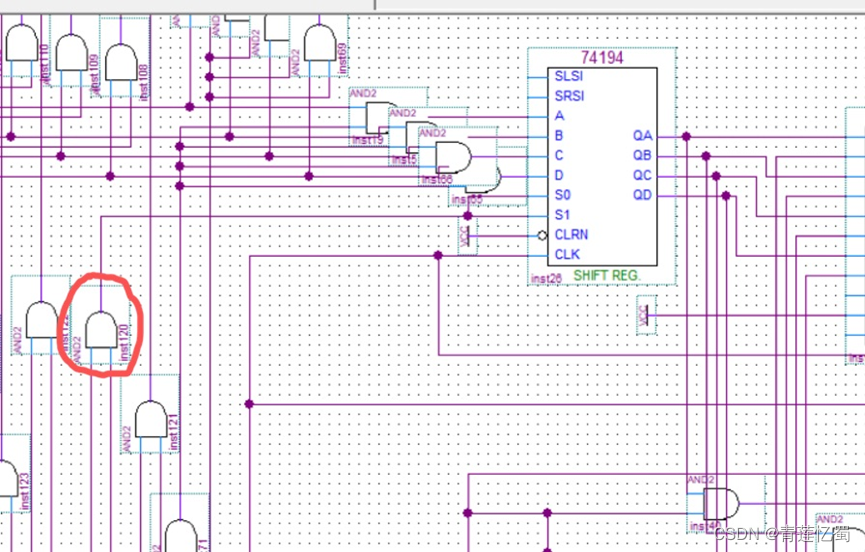

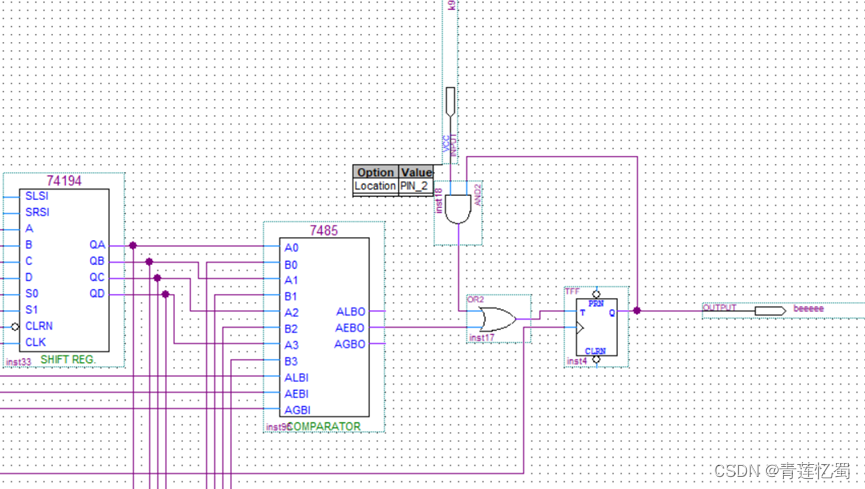

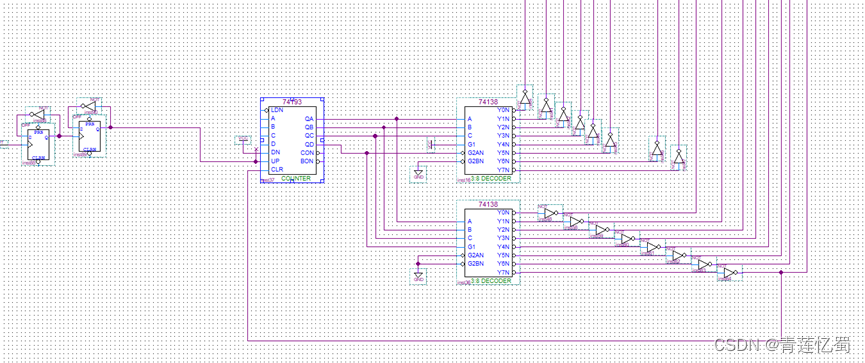

利用74194寄存器存储对应位数的值,存储分、秒共有四位数,因此需要四块74194存储相对应的值

7485数值比较器可以对两数进行比较,用于判断相应位数的值是否完全相等,由于有四位数,因此需要串联四个7485数值比较器对四位数进行比较

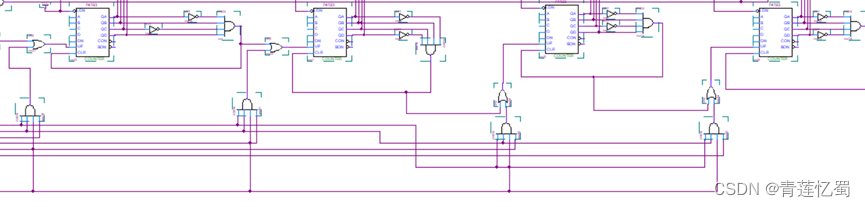

3.4.3电路图

将计数器中的值与寄存器中的值在7485数值比较器中向比较并输出相应地结果

当闹钟开关打开时,通过非门的低电平阻止计数器中的值输出,从而利用或门输出寄存器中的值,达到显示正在设置闹钟的值;相反,当闹钟开关关闭时,寄存器中的值无法输出,只能显示计数器中时钟的数值。

当四个寄存器中的值和计数器的值完全相同时,会在最后AEBO输出高电平。

使用T触发器保持高电平的输出,从而让蜂鸣器持续发声。只有通过手动输入一个高电平,通过T触发器转置,将高电平变成低电平,蜂鸣器停止。

3.4.3 电路图

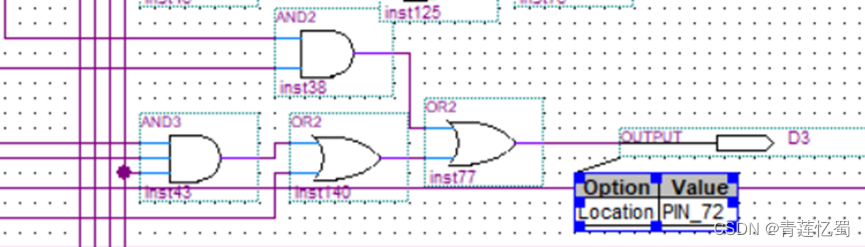

3.5 闪烁模块

3.5.1功能

设置时间时对应位实现闪烁

3.5.2 设计思路和过程

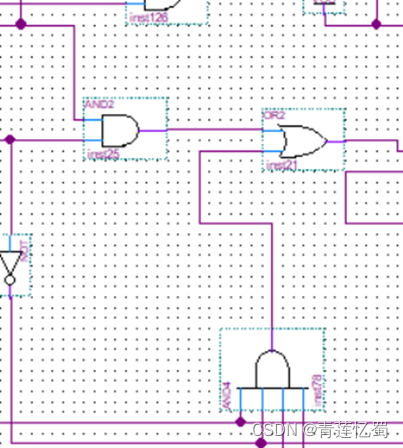

通过实验发现,当8421BCD码超过9时,七段数码管将不再显示任何数字。因此,我们利用这一特性试图做出对应数码位闪烁的特性。

3.5.3电路图

3.6音乐模块

3.6.1功能

播放音乐

3.6.2 设计思路和过程

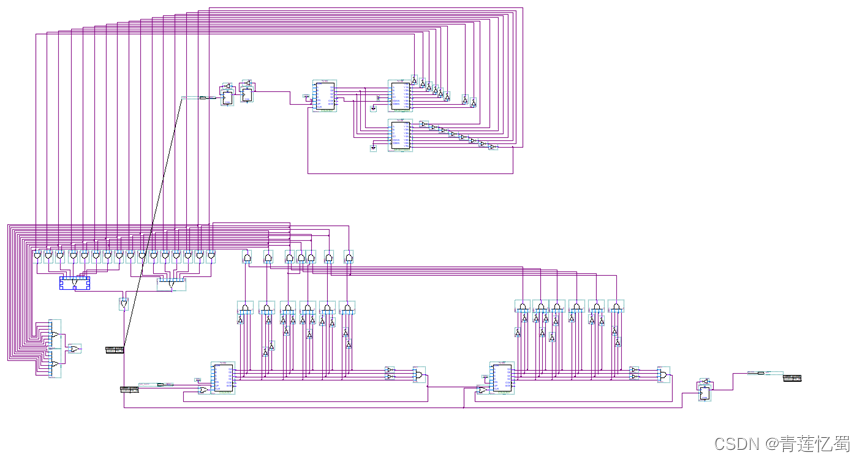

不同的音符是由不同频率振动产生的,对应关系如图所示。我们可以将100KHZ的源频率通过不同的模数计数器转换成不同的频率对应于不同的音符。先使用模XXX计数,得到XXXHZ的频率,再使用模2计数器,进一步降低至(XXX)/2HZ,防止直接模出的频率持续时间很短不足以引起蜂鸣器的振动。此时由于直接连接计数器的Q0 ,所以高电平信号占半个时钟周期,足以驱动蜂鸣器。

这里我们用100KHZ去更加接近模拟音符的频率(如果用低音频当作源频率的话,通过模数计数器,最后会相差十几赫兹)

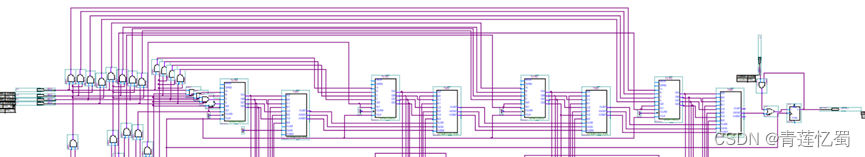

在最开始的设计中,我设计了许多不同的模数计数器,使用了大量的74193计数器,最后编译的时候,报错布线资源不够,芯片资源不够。所以我设计了组合电路,将不同的模数计数器组合在一起。

3.6.3电路图

4. 系统测试

具体的.bdf文件分享

5. 结论

通过一系列讨论和实验,我们基本完成了课程设计要求,实现时钟的基本走时,设置时间、对应位地闪烁、设置闹钟和音乐的设计等功能,但是在实际使用过程中容易发生竞争与冒险,仍存在部分问题。

6. 收获、体会和建议。

通过本次实验,我们对与逻辑电路中的各种仪器有了更近一步的认识,并且熟练掌握了quartus的使用方法,对我们未来的学习有所帮助。同时,我们在讨论过程中,注重对细节的分析和思考,发现和解决了许多问题,使得设计方案更加完善和稳定,但仍然有不小的改善余地,包括优化模拟电路,减少竞争与冒险、实现前认真规划,提高相同功能线路的复用率,使电路图具有更高的可阅读性、优化操作体验等方面。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结