您现在的位置是:首页 >技术交流 >以LAN8720A为例的以太网硬件设计方案网站首页技术交流

以LAN8720A为例的以太网硬件设计方案

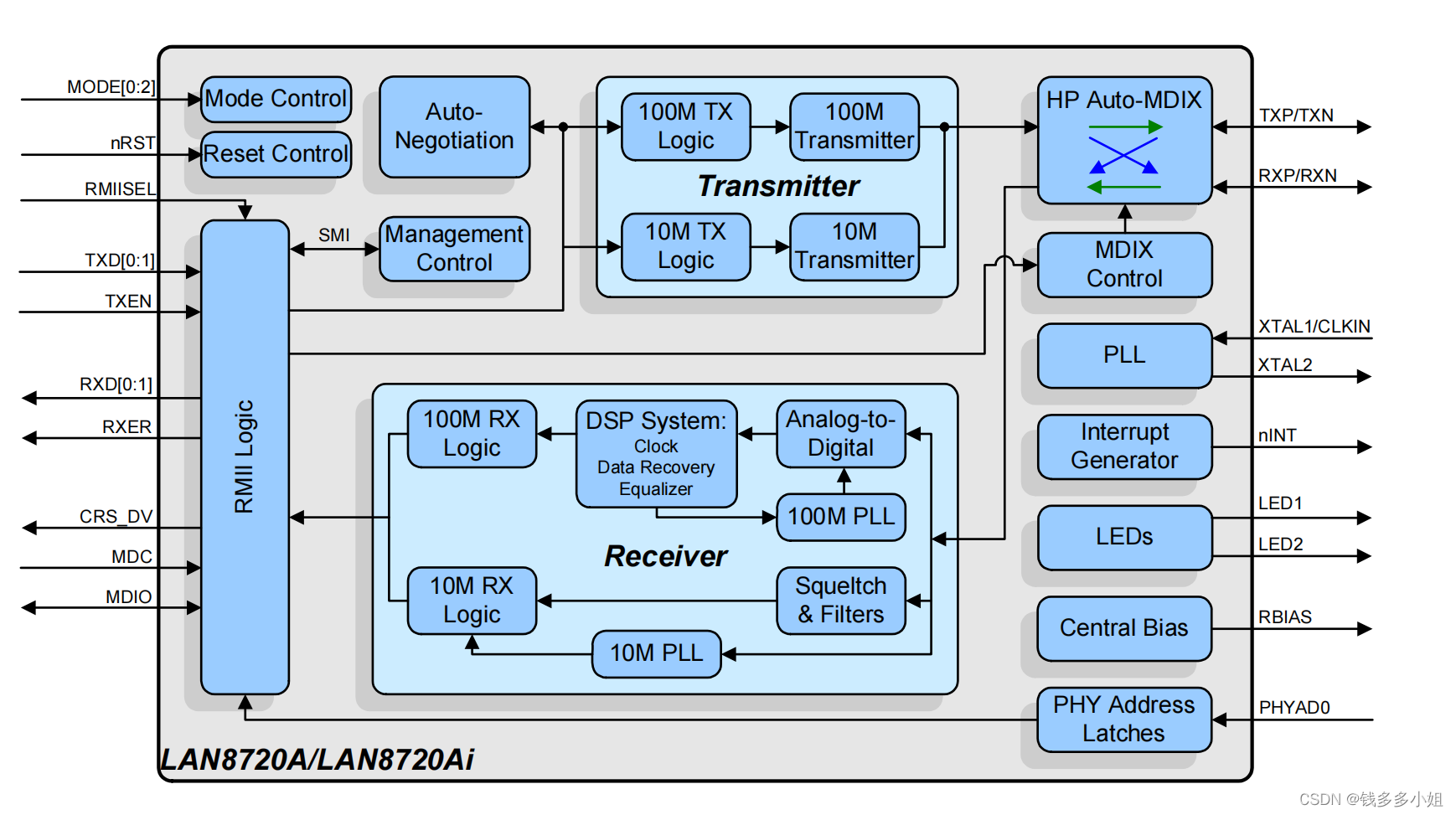

一、芯片概述

芯片主要特点:

1.高性能10/100M以太网传输模块

2.支持RMII接口以减少引脚数

3.支持全双工与半双工模式

4.两个LED状态输出

5.可以使用25MHz晶振以降低成本

6.支持自协商模式

7.支持HP Auto-MDIX自动翻转功能

8.支持SMI串行管理接口

9.支持MAC接口

二、RMII接口概述

注:图中箭头标明数据传输方向

REF_CLK:参考时钟,由MAC或外部时钟晶振向PHY芯片提供

TX_EN:发送始能信号,由MAC向PHY提供

TXD0与TXD1:发送数据位0与1,MAC到PHY

RX_ER:接收数据错误,PHY到MAC

RXD0与RXD1:接收数据位0与1,PHY到MAC

CRS_DV:数据有效标志,PHY到MAC

MDIO:管理数据,双向传输

MDC:管理数据时钟,由MAC提供

三、LAN8720A详解

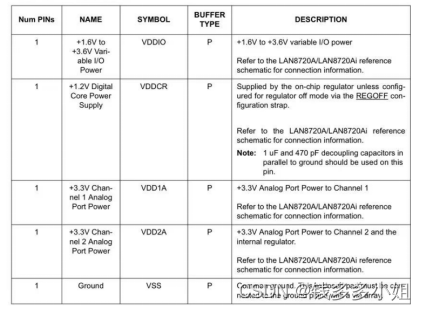

3.1 芯片电源

电源与地分类:

VDDIO:IO引脚供电

VDDCR:1.2V电源,可由芯片内部稳压电源提供,亦可由外部电源提供,由外部电源提供可降低芯片功耗。

VDD1A与VDD2A:为通道1与通道2供电(发送接收通道)

GND:地

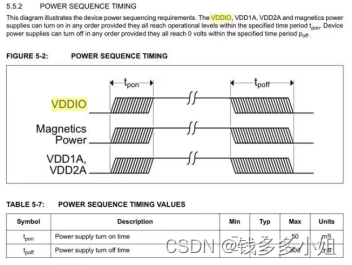

上电时序:

根据手册描述可知:在VDDIO电源至少达到工作电压水平的80% 后,VDDCR方可上电。

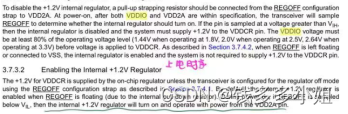

VDDCR上电方式由REGOFF引脚配置,REGOFF接上拉电阻至VDD2A,VDDCR由外部1.2V电源供电。

REGOFF悬空或下拉到地,VDDCR由内部稳压器提供1.2V电源。

VDDIO与VDD1A,VDD2A只要在规定时间段tpon内达到工作电压水平,就可以按照任意顺序接通。

3.2芯片时钟

输入时钟(XTAL1/CLKIN,XTAL2):推荐外加25MHz(性价比较高)晶振为PHY芯片提供时钟,PHY芯片内部PLL将其倍频为50MHz来使用,亦可使用直接使用50MHz晶振。

输出时钟(REFCLKO):向MAC端输出50MHz时钟。

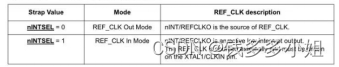

nINTSEL引脚决定 REFCLKO时钟来源,nINTSEL=0,采用REF_CLK Out Mode模式,REFCLKO由PHY内部PLL提供。nINTSEL=1,采用REF_CLK In Mode模式,REFCLKO由外部晶振提供,此情况下外部晶振需选用50MHz。

3.3芯片复位

复位引脚(nRST):低有效。

3.4余下配置

3.4.1 MODE配置

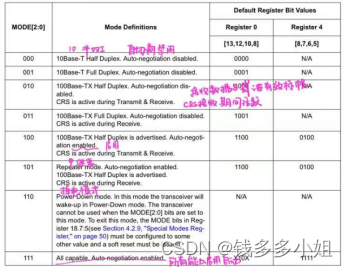

MODE配置:以太网传输速率及工作方式配置

三位MODE通过高低电平组合分别对应以上8种模式 ,包含10M半双工,10M全双工,100M半双工,100M全双工,是否启用自协商协议,CRS是否有效等。

3.4.2 PHY地址配置

PHY地址引脚(PHYAD0):通过该引脚对器件SMI地址进行配置。

3.4.3 RBIAS引脚配置

外部偏置电阻(RBIAS):外接12.1KΩ电阻下拉到地,为芯片内部提供参考。

3.4.5 LED的使用

LED1:检测到有数据传输点亮,检测到CRS高电平,闪烁。

LED2:检测到数据以100M传输,点亮。

手册链接:链接:https://pan.baidu.com/s/1yV5kbN-ysZBi_ZLoEh5ywA

提取码:wxm9

U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结