您现在的位置是:首页 >技术教程 >带有时钟使能和同步清零的D触发器网站首页技术教程

带有时钟使能和同步清零的D触发器

简介带有时钟使能和同步清零的D触发器

每个 Slice 有 8 个 FF 。四个可以配置为 D 型触发器或电平敏感锁存器,另外四个只能配置为 D 型触发器,但是需要记得是:当原来的四个 FF 配置为锁存器时,不能使用这四个 FF 。

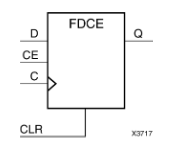

(1)FDCE

简介

带有时钟使能和异步清零的 D 触发器

当时钟使能(CE)为高并且异步清零信号 CLR 为低时,该 D 触发器将数据输入 D 端传递到输出 Q 端。

当CLR为高,不管输入是什么,输出 Q 端值为 0。

原语

FDCE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDCE_inst (.Q(Q), // 1-bit Data output.C(C), // 1-bit Clock input.CE(CE), // 1-bit Clock enable input.CLR(CLR), // 1-bit Asynchronous clear input.D(D) // 1-bit Data input);

真值表

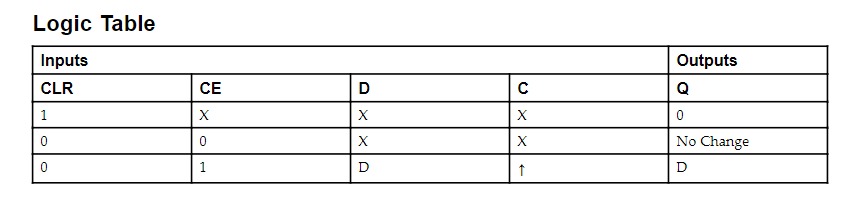

(2)FDPE

简介

带有时钟使能和异步置位的 D 触发器

当时钟使能(CE)为高并且异步置位信号 PRE 为低时,该 D 触发器将数据输入 D 端传递到输出 Q 端。当 PRE 为高,不管输入是什么,输出 Q 端值为 1。

原语

FDPE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDPE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .PRE(PRE), // 1-bit Asynchronous preset input .D(D) // 1-bit Data input);

真值表

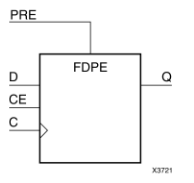

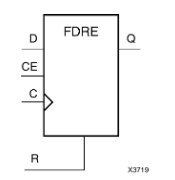

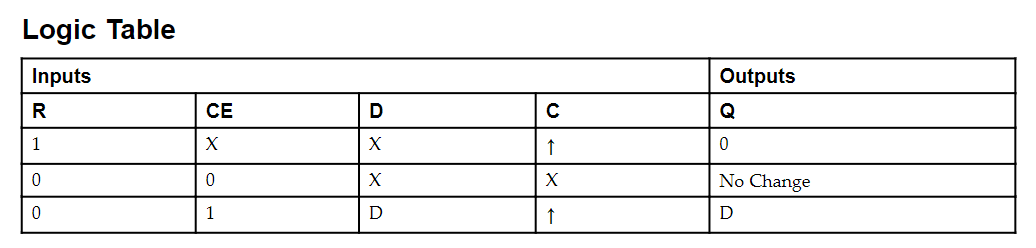

(3)FDRE

简介

带有时钟使能和同步清零的 D 触发器

当时钟使能(CE)为高并且同步清零信号 R 为低时,该 D 触发器在时钟上升沿将数据输入 D 端传递到输出 Q 端。

当 R 为高,不管输入是什么,输出 Q 端值为 0。

原语

FDRE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDRE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .R(R), // 1-bit Synchronous reset input .D(D) // 1-bit Data input);

真值表

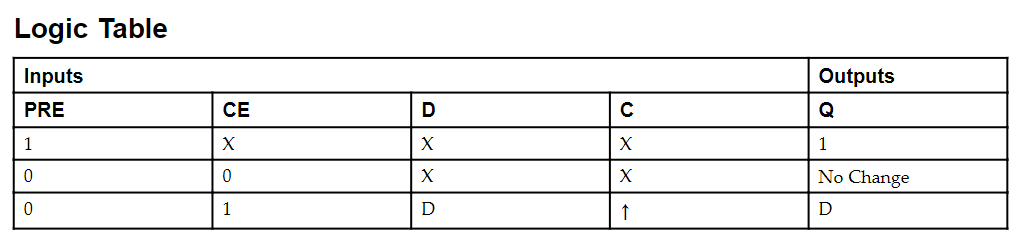

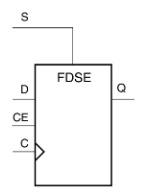

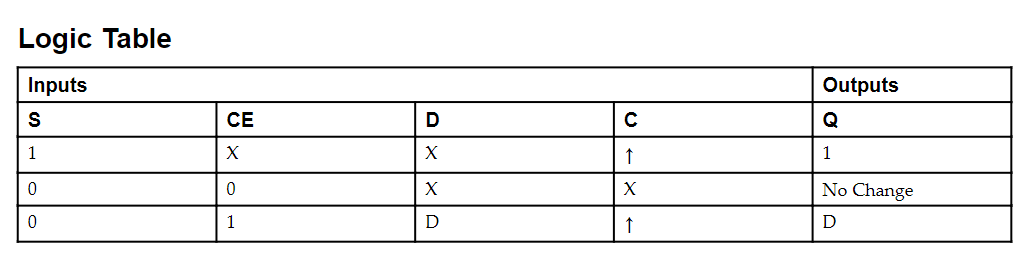

(4)FDSE

简介

带有时钟使能和同步置位的 D 触发器

当时钟使能(CE)为高并且同步置位信号 S 为低时,该 D 触发器在时钟上升沿将数据输入 D 端传递到输出 Q 端。

当 S 为高,不管输入是什么,输出 Q 端值为 1。

原语

FDSE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDSE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .S(S), // 1-bit Synchronous set input .D(D) // 1-bit Data input);

真值表

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结