您现在的位置是:首页 >其他 >ZYNQ-Linux开发之(一)(Vivado - C2C使用)网站首页其他

ZYNQ-Linux开发之(一)(Vivado - C2C使用)

目录

该文档主要介绍vivado中C2C IP核的使用,包括应用场景,block design中接线,C++代码中操作使用等。

C2C目前嵌入式使用的用途就是和FPGA进行通信,替代之前的SPI通信,C2C的好处是速度快,稳定,传输错误率比SPI低,vivado中需要搭配Aurora使用。

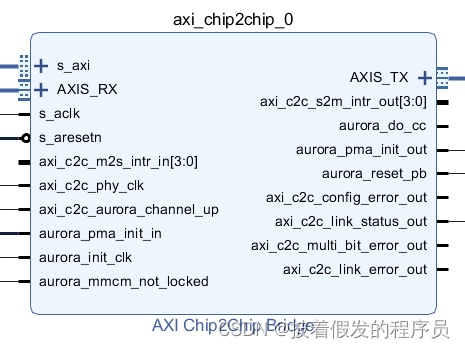

简单介绍下重要的引脚,详细介绍大家可以去阅读官方手册

axi_c2c_aurora_channel_up:标志着C2C的状态,channel_up为1,代表硬件层链路通

axi_c2c_link_status_out:标志着两端C2C的连接状态,为1代表已经可以传输数据。

如果搭建好工程后测试不通,可对这两个引脚抓下debug,查看状态是否正常。

其余是一些时钟和复位引脚,详细可查手册

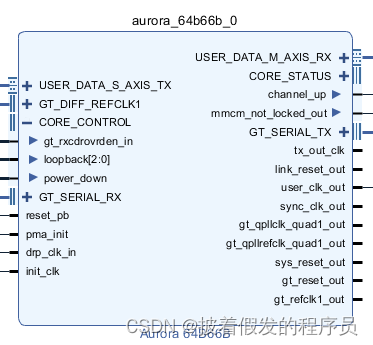

与C2C相连的Aurora的IP核

channel_up:重点关注引脚,为高电平代表两端的Aurora硬件层已通。

GT_SERIAL_RX:serdes接收方向

GT_SERIAL_TX:serdes发送方向

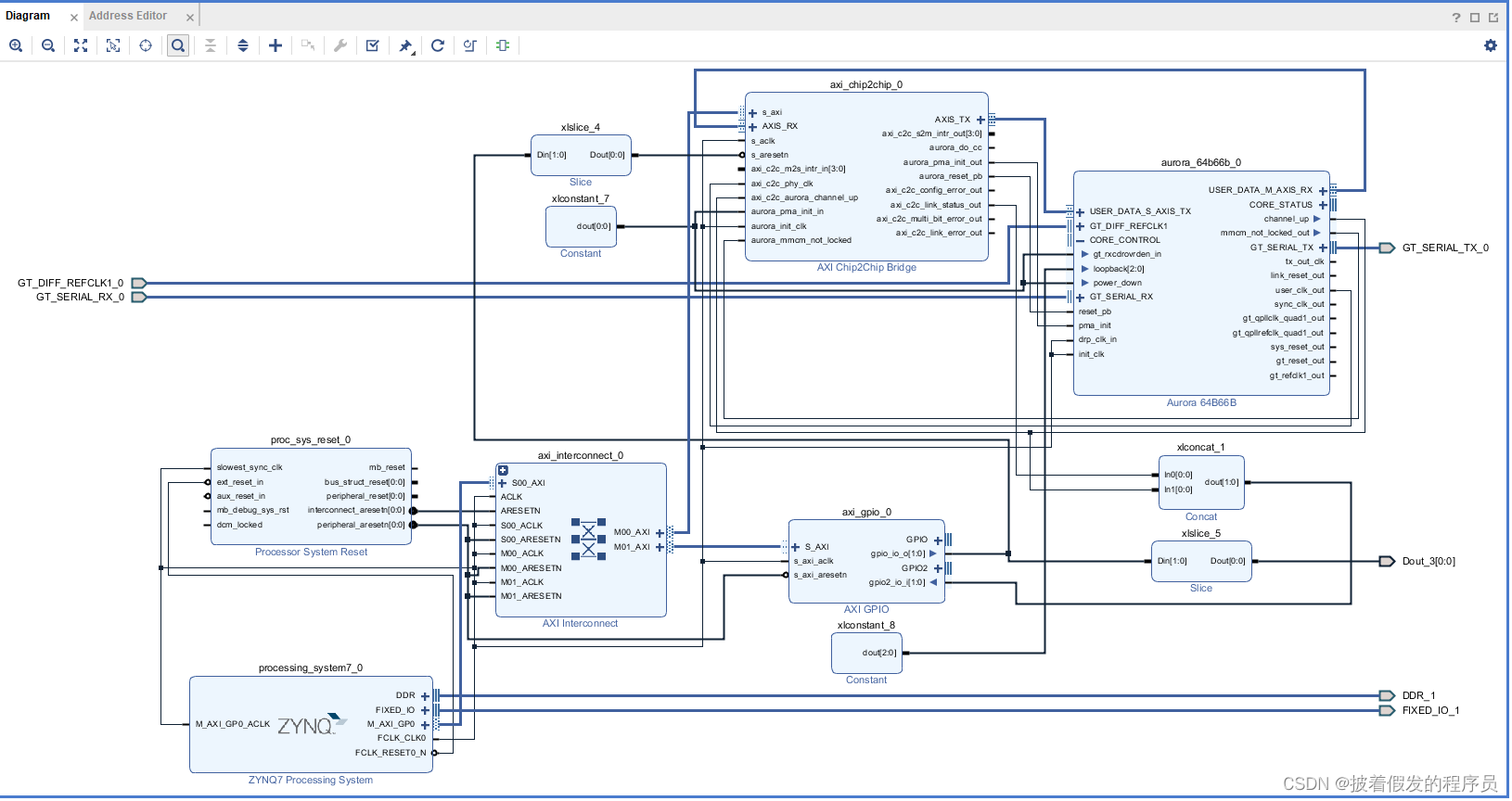

搭建工程时。可按图中对IP核进行配置,但是很多参数还是需要注意的,例如Data Width,Address Width等,需要与FPGA端的配置保持一致,尤其是ID Width,与FPGA端不一致的话,可能会导致用C2C写数据时linux系统崩溃。

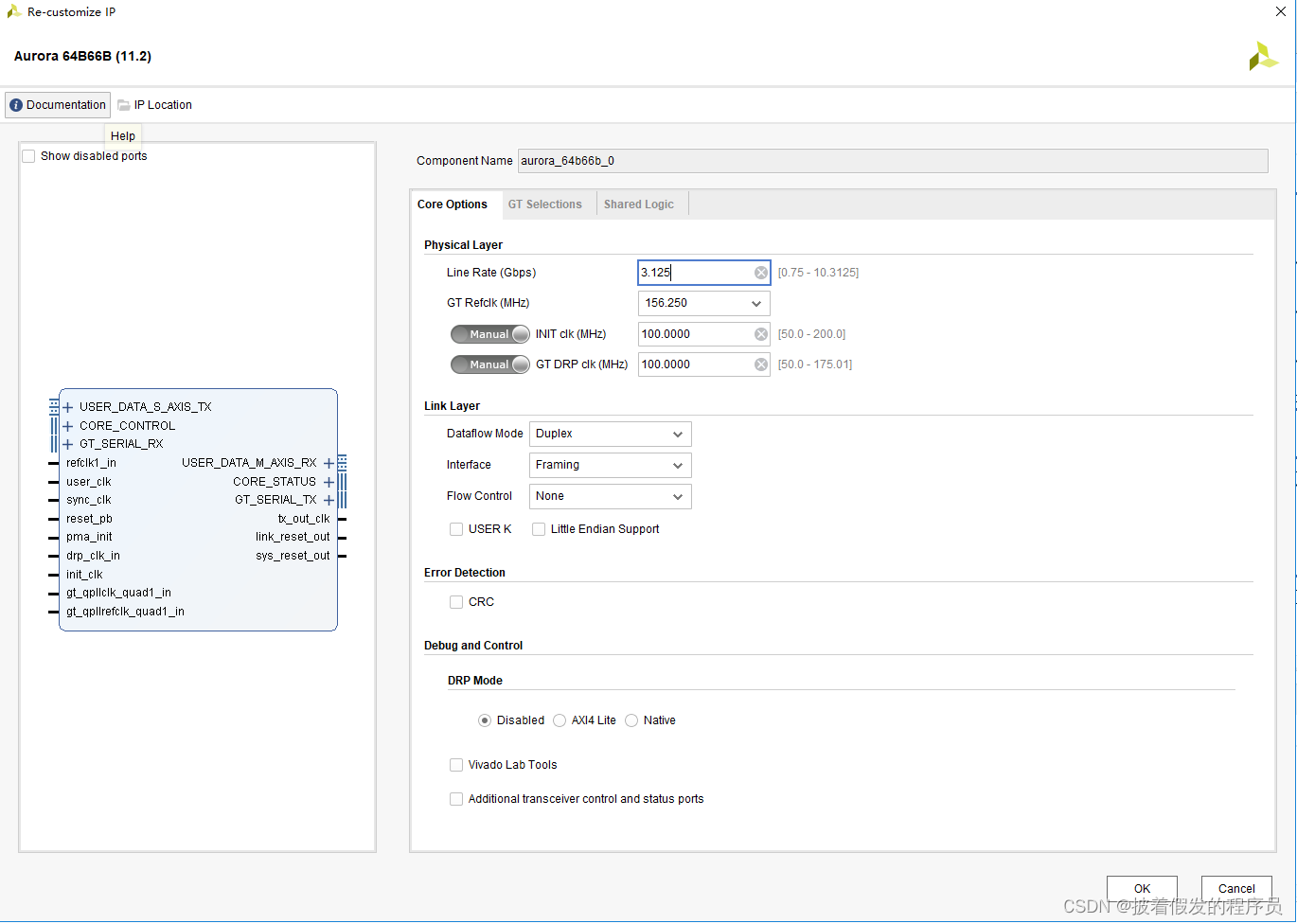

C2C需要配合Aurora IP核使用,此时Aurora IP核做如下配置,如果FPGA端有哪些参数与这些不同,按照FPGA端的参数进行修改,除了GT Refclk以外,其余都要相同,要确保每个参数与FPGA端的aurora的参数一致,否则可能无法使用。

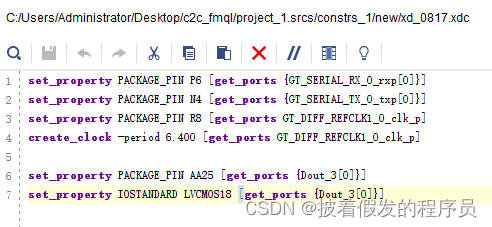

对应的XDC约束文件,其中

Dout_3[0]为给FPGA端C2C复位的GPIO

GT_SERIAL_RX_0_rxp和GT_SERIAL_RX_0_txp为serdes约束

GT_DIFF_REFCLK1_0_clk_p为时钟约束

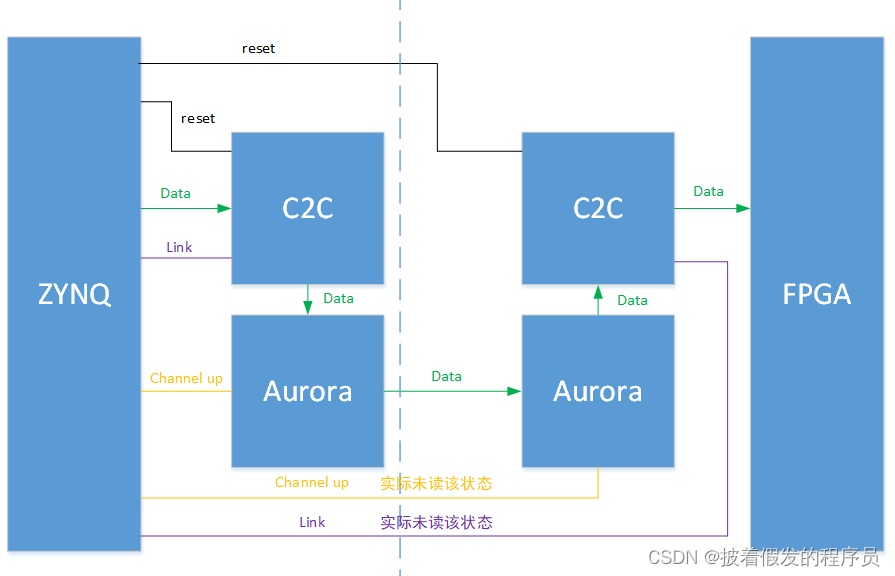

chip to chip的连接框图大致如下,ZYNQ与FPGA双方的IP核是对称的,数据从ZYNQ经过ZYNQ端的c2c(master)、ZYNQ端的aurora、FPGA端的aurora、FPGA端的c2c(slave)最后到FPGA。

ZYNQ需要控制是ZYNQ端的c2c复位和FPGA端的c2c,需要先复位FPGA端的c2c(slave)再复位ZYNQ端的c2c(master)。复位过程先拉低FPGA端的c2c复位管脚,再拉低ZYNQ端的c2c复位管脚,然后拉高FPGA端的c2c复位管脚和ZYNQ端的c2c复位管脚。

ZYNQ读写c2c前,需要先判断link和channel up信号,均为1时表示已就绪可以进行读写操作,否则会出现ZYNQ系统挂掉的情况。理论上需要获取ZYNQ端和FPGA端的link及channel up,实际操作时只读取ZYNQ端的即可。

reset、Link和channel up管脚从内部约束到ZYNQ引脚,可能是分别约束到ZYNQ的普通GPIO管脚,也可以约束到ZYNQ的AXI GPIO管脚。普通GPIO管脚和AXI GPIO管脚的操作略有不同,分别使用框架中的CGPIOHandle和CAxiGPIOHandle类操作方法。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结