您现在的位置是:首页 >学无止境 >5.dsp-ADC采样网站首页学无止境

5.dsp-ADC采样

目录

(1)SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1;

(2)SysCtrlRegs.HISPCP.all = ADC_MODCLK;

(5)AdcRegs.ADCTRL2.all = 0x2000;

当需要采集外部信号时,外部信号多数是模拟信号,如电压、电流、压力、 温度、湿度、速度等,而单片机又只能处理数字信号,因此就需要一个将模拟信 号转换为数字信号的介质--模数转换器(ADC)。普中dsp教程学习总结。

1. ADC 转 换 步 骤

AD 转 换 器 (ADC) 将 模 拟 量 转 换 为 数 字 量 通 常 要 经 过 4 个 步 5 : 采 样 、 保持 、 量化、编码 。 所 谓 采 样 即 是 将 一 个 时 间 上 连 续 变 化 的 模 拟 量 转 换 为 时 间 上 离 散 变 化 的 模 拟 量 。 采样是指以一定的时间间隔对模拟信号进行一次取样,将模拟信号转化为离散序列;将 采 样 结 果 存 储 起 来 , 直 到 下 次 采 样 , 这 个 过 程 叫 做 保 持 。 一 般 采 样 器 和 保持电路一 起 总 称 为 采 样 保 持 电 路 。 将 采 样 电 平 归 化 为 与 之 接 近 的 离 散 数 字 电 平 ,过 程 叫 做 量 化 量化是将采样得到的离散样本转换为离散的数值;编码是将量化好的离散数值二进制编码,输出数字信号。

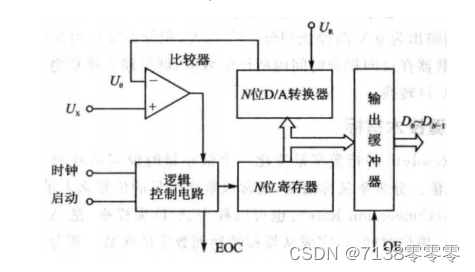

将 采 样 电 平 ( 模 拟 值 ) 转 换 为 数字值 时 , 主 要 有 两 类 方 法 : 直 接 比较 型 与 间 接 比 较 型 。

一 直 接 比较型:将 输 入 模 拟 信 号 直 接 与 标 准 的 参 考 电 压 比 较 , 而 得到数字量, 常 见 的 有 并 行 A DC 和 逐次比较型ADC。

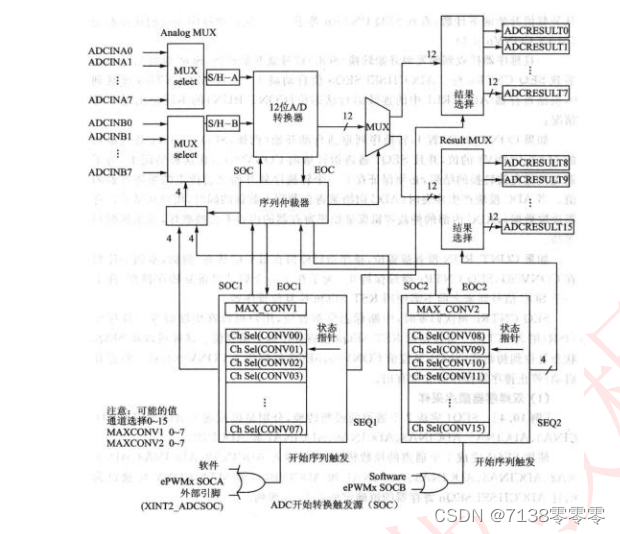

图中EOC的全称为 End of Conversion,即转换结束的意思,是指ADC转换完成后会出发EOC信号。当它变为1时,表示ADC转换完成,数据已经准备好可以读取了。根据EOC信号,在程序中可以触发相应的中断服务程序或采取其他的处理方式,以完成数据读取、存储、处理等操作。

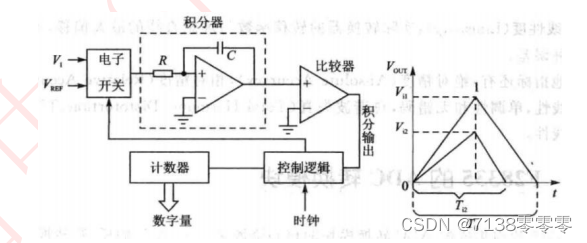

一 间 接 比 较 型 : 输 入 模 拟 量 不 是 直 接 与 参 考 电 压 比 较 , 而 是 将 二 者 变 为 中 间 的 某 种 物 理 量 在 进 行 比 较 , 然 后 将 比 较 所 得 的 结 果 进 行数 字 编 码 。 常 见 的 有 双 积 分 型 ADC。

2、ADC的核心技术指标

(1)分辨率

(2)转换速率

(3)量化误差

(4)偏移误差

(5)满刻度误差

(6)线刻度

3、ADC介绍

F28335 片内集成的 ADC 转换模块的核心资源是一个 12 位的模数转换器,这 个精度已经能够满足大多数测量需要,如果需要用到更高精度的 AD,比如 16 位 或者 24 位的,就需要外扩高精度的 AD 芯片。

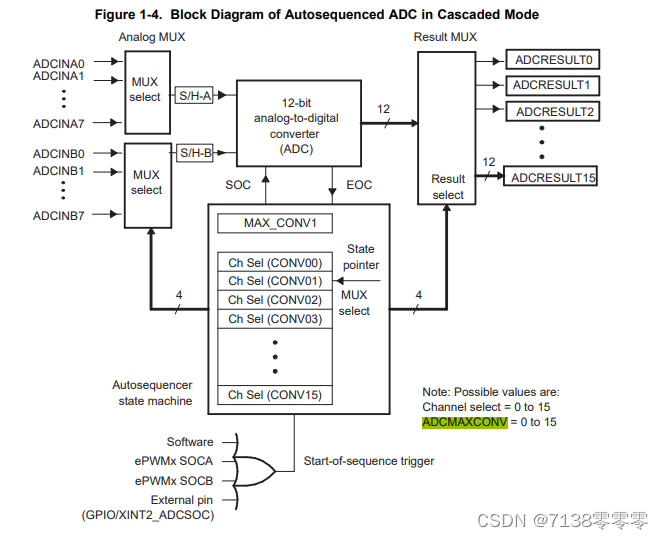

F28335 ADC 转换模块具有 16 个通道,由 2 个独立的 8 通道模块组成,这两 个独立的 8 通道模块也可以级联成一个 16 通道模块。尽管 AD 转换器中有多个输 入通道和两个序列发生器,但只有一个转换器。由此需要排序器。

两个 8 通道模块能够自动排序构成一系列转换器,每个模块可以通过模拟的 多路开关(MUX)选择 8 个通道中的任何一个通道。在级联模式下,自动序列发 生器是 16 通道的。对每一个序列发生器而言,一旦完成转换,所选通道的转换 值将存储到相应的 ADCRESULT 寄存器中。自动排序过程允许系统对同一个通道进 行多次变换,允许用户进行过采样算法从而得到比一般的单采样更精确的结果。

表1 排序器触发源

由上图可知F28335 的 ADC 模块主要包括以下特点:

--12 位模数转换

--2 个采样保持器(S/H)

--同时或顺序采样

--模拟电压输入范围 0-3V

--ADC 转换时钟频率最高可配置为 25MHz,采样带宽 12.5MHz

--16 通道模拟输入

--排序器支持 16 通道独立循环“自动转换”,每次转换通道可以软件编程 选择。

--16 个结果寄存器存放 ADC 转换的结果,转换后的数字量表示为: 数字值=4095*(输入模拟值-ADCLO)/3,输入模拟值在 0-3V 之间

--多个触发源启动 ADC 转换(SOC):①S/W--软件立即启动 ②外部引脚 ③ePWMx SOCA 启动 ④ePWMx SOCB 启动

--灵活的中断控制,允许每个或者每隔一个序列转换结束产生中断请求

--排序器可工作在启动/停止模式

-采样保持(S/H)采集时间窗口有独立的预定标控制

4、排序器工作原理

排序器分为:单排序器方式、双排序器方式

采样分为:顺序采样、同步采样

两种排序工作方式都可以进行顺序采样或 者同步采样,两种采样方式最大的不同在于,顺序采样相当于串行模式,同步采 样相当于并行模式,能保证信号的同时性,显然同步采样的要求高一些,两个采 样保持器,决定了最多能够进行 2 路同步,在这电气常用控制中,跟 PWM 控制结 合起来很有用,但超过 2 路同步就无能为力了。采样的时候可以多次采样,然后取平均,以获得比单采样方式更精确的结果。

两种操作方式的最大差别就在于,单排序操作方式(级联方式)响应触发源是唯一的,可双排序的方式可以分别响应各自的触发源。单排序操作方式简单,双排序操作方式复杂。

(1)单排序器

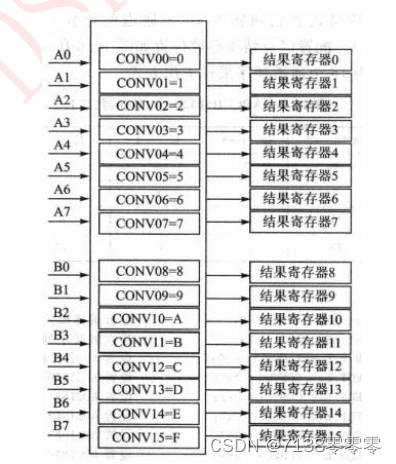

级联位1 个 16位 状态排序器,启动 ADC 之前,首先要进行一些初始化的工作。初始化转换的最多通道数 (MAX_CONV),这个参数限制了最多有效通道数,对于级联模式,最大为 16。

假如输入信号为 6,设置值为 4,实际只有 4 个输 入有效通道。配置需要的转换输入信号对应的转换次序(CHSELxx),最终的转换结果存放在各自的结果寄存器

(RESULT0-RESULT15),结果寄存器不与输入通道完全对应,而是结果寄存器与转换次序对应。16 通道对应结果寄存器如下:

(2)双排序器

2 个独立的 8 状态排序器,当 ADC 工作在双排序器工作方式下时,2 个 8 状态排序器(SEQ1 和 SEQ2)彼 此独立。在这种方式下 PWMA 触发 SEQ1,PWMB 触发 SEQ2,触发源是独立的。双 排序器工作方式可以将 ADC 看成两个独立的 AD 转换单元,每个单元由各自的触 发源触发转换。

SEQ1 排序器有更高的优先级,如果 SEQ1 和 SEQ2 的 SOC 请求都没有挂起,并且 SEQ1 和 SEQ2 同时产生 SOC 请求,则 ADC 完成 SEQ1 的有效排序后,将会立即处理新的 SEQ1 的转换请求,SEQ2 的转换请求处于挂起状态。

每个排序器中的转换通道个数依然受 MAXCONVn 控制,最大控制通道数为 7, 而不是前面的 16。该值在自动排序转换的开始时被载到自动排序状态寄存器 (AUTO_SEQ_SR)的排序计数器控制位(SEQ CNTR3-0),MAX CONVn 的值在 0-7 内变化。当排序器安排内核从 CONV00 开始按顺序转换时,SEQ CNTRn 的值从装 载值开始向下计数,直到 SEQ CNTRn 为 0.一次自动排序完成的转换数为 MAXCONVn+1。

(3)采样

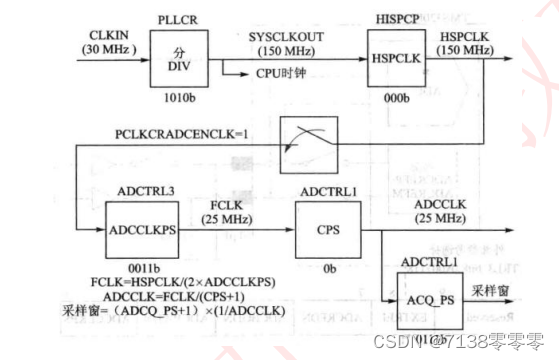

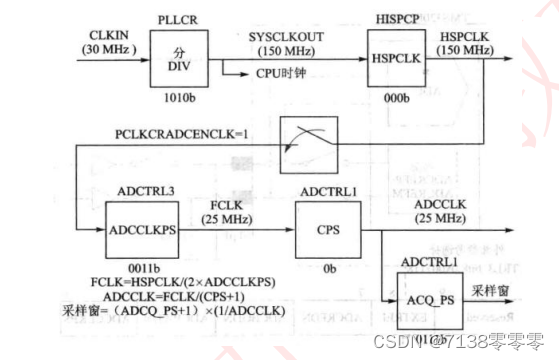

5、ADC时钟

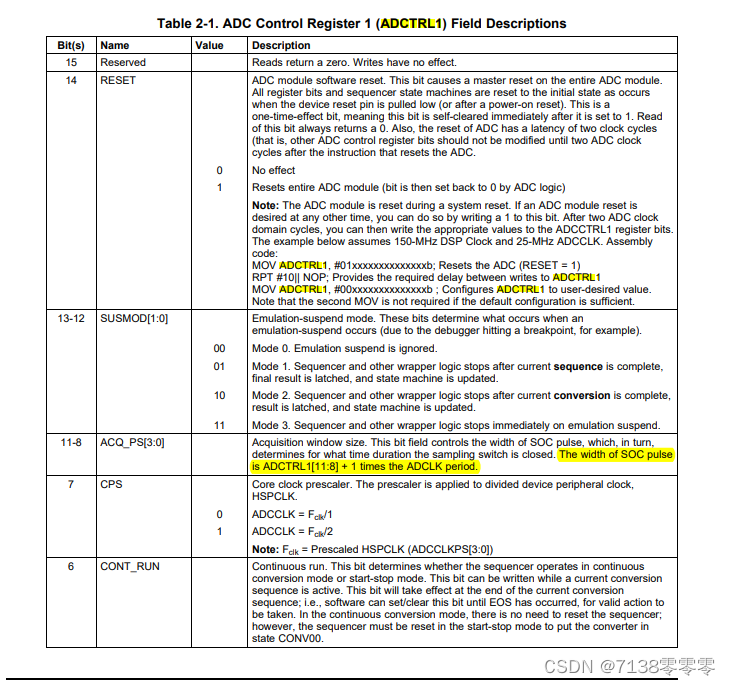

外设时钟 HSPCLK 是通过 ADCTRL3 寄存器的 ADCCLKPS[3-0]位来分频的,然后 再通过寄存器 ADCTRL1 中的 CPS 位进行 2 分频或者不分频。此外,ADC 模块还通 过扩展采样获取周期调整信号源阻抗,这由 ADCTRL1 寄存器中的 ACQPS3-0 位控制。

6、相关寄存器及代码分析

(1)ADC 相 关 寄 存 器

( a ) ADC 模 块 控 制 寄 存 器 1 (ADCTRLI)

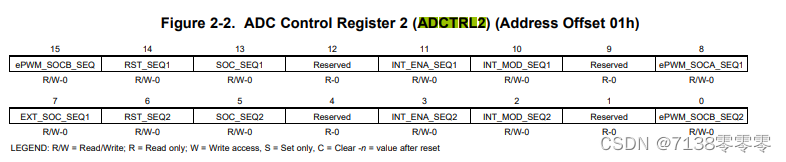

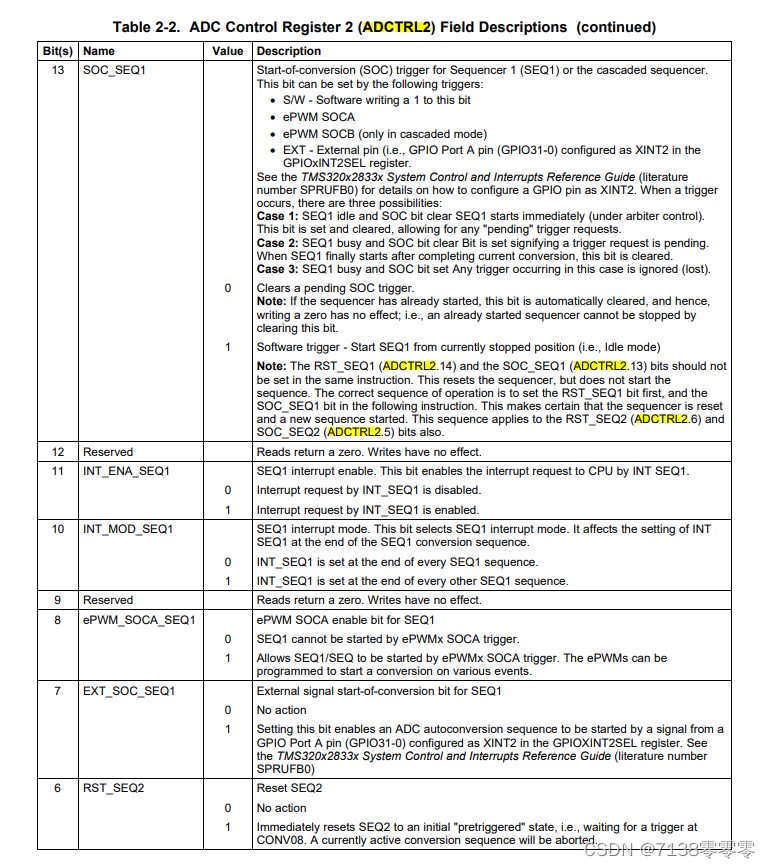

( b) ADC 模 块 控 制 寄 存 器 2 (ADCTRL2)

( c ) ADC 模 块 控 制 寄 存 器 3 (ADCTRL3)

( d ) 最 大 转 换 通 道 数 (ADCMAXCONV)

( e ) 自 动 排 序 状 态 寄 存 器 (ADCASEQSR)

( f ) ADC 状 态 和 标 志 寄 存 器

( g ) ADC 输 入 通 道 选 择 排 序 控 制 寄 存 器

( h ) 结 果 寄 存 器 (ADCRESULTn)

7、相关寄存器及代码分析

void ADC_Init(void)

{

// Specific clock setting for this example:

EALLOW;

SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; // ADC

EDIS;

// Specific clock setting for this example:

EALLOW;

SysCtrlRegs.HISPCP.all = ADC_MODCLK; // HSPCLK = SYSCLKOUT/(2*ADC_MODCLK)

EDIS;

InitAdc(); // For this example, init the ADC

// Specific ADC setup for this example:

AdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;

AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;

AdcRegs.ADCTRL1.bit.SEQ_CASC = 1; // 1 Cascaded mode

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;

AdcRegs.ADCTRL1.bit.CONT_RUN = 1; // Setup continuous run

AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x0;

// Start SEQ1

AdcRegs.ADCTRL2.all = 0x2000;

}(1)SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1;

使用ADC这条线需要先使能ADC时钟,通过数据手册可以知道具体对应位。

(2)SysCtrlRegs.HISPCP.all = ADC_MODCLK;

令HISPCP等于3,满足ADC时钟要求。

令HISPCP等于3,满足ADC时钟要求。

(3) InitAdc();

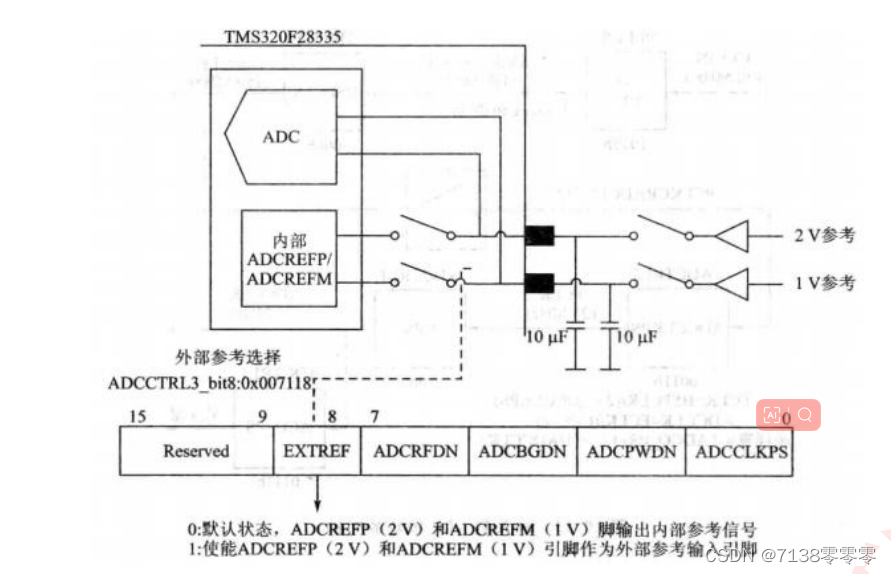

使用 ADC 时除了开启外设时钟外,还需要对参考电 压寄存器设置,并且在 ADC 开始转换前需要一定的延时。

(4)AdcRegs.

ADC 工作方式设置,包括采样方式、工作频率、采样通道数等。

AdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;

AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;

AdcRegs.ADCTRL1.bit.SEQ_CASC = 1; // 1 Cascaded mode

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;

AdcRegs.ADCTRL1.bit.CONT_RUN = 1; // Setup continuous run

AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x0;

图 ADC作用寄存器

ADCTRL1寄存器:

设置AdcRegs.ADCTRL1.bit.ACQ_PS = 3; 是将ADC模块中ADCTRL1寄存器的ACQ_PS位设置为3,表示设置采样窗口延迟时间为3。在F28335的ADC模块中,采样窗口延迟时间表示在采样时,从发出采样请求到实际开始采样的时间间隔。采样窗口延迟时间越短,采样的延时就越小,ADC采样的精度就越高。ACQ_PS的取值范围为0~31,实际延迟时间= ACQ_PS × 1/ADC时钟周期。因此,当ACQ_PS设置为3时,采样窗口延迟时间大致为3个ADC时钟周期。

F28335中的ADC模块的ADCTRL1寄存器是一个控制寄存器,用于控制ADC的各种参数。下面是ADCTRL1中各个位的含义和设置方法:

- bit 15: 置1,使能ADC模块

- bit 14-13: 设置 ADC采样窗口的开关,一般置 11

- bit 12-8: 设置 ADC采样窗口的延迟时间,取值范围为0~31,一般置 0

- bit 7: 设置 ADC采样触发源,0表示软件触发,1表示硬件触发

- bit 6-5: 设置 ADC采样分辨率,00表示12位,01表示10位,10表示8位,11表示6位

- bit 4: 设置 ADC信号输入模式,0表示单端输入,1表示差分输入

- bit 3-2: 设置 ADC信号采样窗口模式,00表示信号不通过采样窗口,01表示小于采样窗口的信号不被采集,10表示大于采样窗口的信号不被采集,11表示位于采样窗口内的信号被采集

- bit 1-0: 设置 ADC转换结果的格式,00表示16位二补码格式,01表示16位补码格式,10表示32位二补码格式,11表示32位补码格式

例如,如果要使用单端输入模式、12位分辨率、软件触发、采样窗口模式为“信号不通过采样窗口”以及16位二补码结果格式,可以设置ADCTRL1为0x0。

代码示例:

AdcRegs.ADCTRL1.bit.ADCENABLE = 1; //使能ADC模块

AdcRegs.ADCTRL1.bit.CONT_RUN = 0; //设置采样窗口控制开关

AdcRegs.ADCTRL1.bit.ACQ_PS = 0; //设置采样窗口延迟时间

AdcRegs.ADCTRL1.bit.SEQ_CASC = 0; //设置序列重复采样

AdcRegs.ADCTRL1.bit.SEQ_OVRD = 0; //设置序列覆盖方式

AdcRegs.ADCTRL1.bit.SOC_SEQ = 0; //选择采样模式为软件触发

AdcRegs.ADCTRL1.bit.SEQ_OVRD = 0; //关闭序列覆盖方式

AdcRegs.ADCTRL1.bit.SEQ_CASC = 0; //关闭序列重复采样

AdcRegs.ADCTRL1.bit.CONT_RUN = 0; //设置采样窗口控制开关

AdcRegs.ADCTRL1.bit.SIMULEN0 = 0; //选择单端输入模式

需要注意的是,采样窗口延迟时间的具体设置取决于芯片的处理速度和输入电信号的变化速度,需要根据实际情况而定。

ADCTRL3寄存器:

ADCCHSELSEQ1寄存器:

ADCMAXCONV寄存器:

(5)AdcRegs.ADCTRL2.all = 0x2000;

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结