您现在的位置是:首页 >其他 >ARM体系结构与异常处理网站首页其他

ARM体系结构与异常处理

目录

一、ARM体系架构

1、ARM公司概述

ARM的含义

ARM(Advanced RISC Machines)有三种含义 :一个公司的名称、一类处理器的通称、一种技术

ARM公司

> 成立于1990年11月,前身为Acorn计算机公司

> 主要设计ARM系列RISC处理器内核

> 授权ARM内核给生产和销售半导体的合作伙伴,ARM公司并不生产芯片

> 提供基于ARM架构的开发设计技术软件工具、评估板、调试工具、应用软件、 总线架构、外围设备单元等

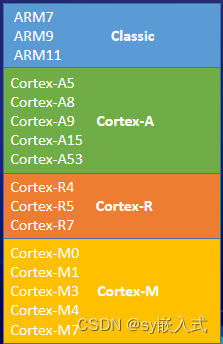

2.ARM产品系列

早先经典处理器

包括ARM7、ARM9、ARM11家族

Cortex-A系列

针对开放式操作系统的高性能处理器 应用于智能手机、数字电视、智能本等高端运用

Cortex-R系列

针对实时系统、满足实时性的控制需求 应于汽车制动系统、动力系统等

Cortex-M系列

为单片机驱动的系统提供了低成本优化方案 应用于传统的微控制器市场、智能传感器、汽车周边等

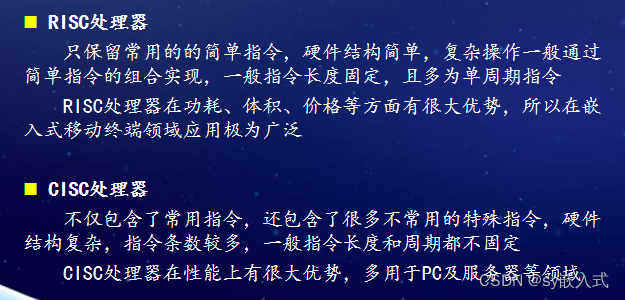

RISC精简指令集,代表:ARM

CISC:复杂指令集,典型代表:Intel

SOC(System on Chip) 即片上系统,将一个系统中所需要的全部部件集成在一个芯片中在体积、功耗、价格上有很大优势。例如:单片机

3.指令、指令集

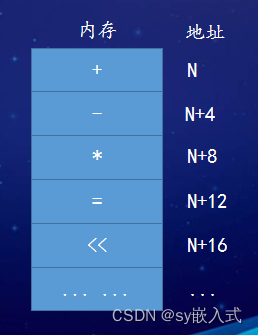

指令

能够指示处理器执行某种运算的命令称为指令(如加、减、乘 ...)

指令在内存中以机器码(二进制)的方式存在

每一条指令都对应一条汇编

程序是指令的有序集合

指令集

处理器能识别的指令的集合称为指令集

不同架构的处理器指令集不同

指令集是处理器对开发者提供的接口

ARM指令集

大多数ARM处理器都支持两种指令集:

ARM指令集 (属于RISC精简指令集)

所有指令(机器码)都占用32bit存储空间

代码灵活度高、简化了解码复杂度

执行ARM指令集时PC值每次自增4

Thumb指令集 (ARM指令集子集)

所有指令(机器码)都占用16bit存储空间

代码密度高、节省存储空间

执行Thumb指令集时PC值每次自增2

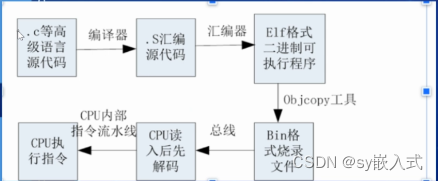

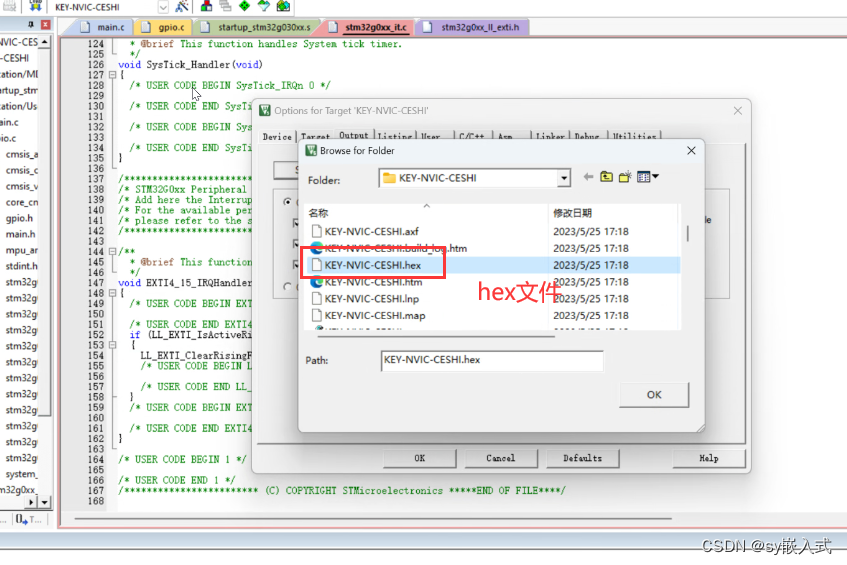

4.编译原理

单片机常用的烧录二进制格式hex文件

机器码(二进制0 1)是处理器能直接识别的语言,不同的机器码代表不同的运算指令,处理器能够识别哪些机器码是由处理器的硬件设计所决定的,不同的处理器机器码不同,所以机器码不可移植

汇编语言是机器码的符号化,即汇编就是用一个符号来代替一条机器码,所以不同的处理器汇编也不一样,即汇编语言也不可移植

-

-S: 编译,生成汇编代码,生成的文件为

test.Sgcc -S test.s

-

-c: 汇编:生成机器码,生成的文件未

test.ogcc -c test.c

C语言在编译时我们可以使用不同的编译器(gcc)==>(翻译官)将C源码编译成不同架构处理器的汇编,所以C语言可以移植

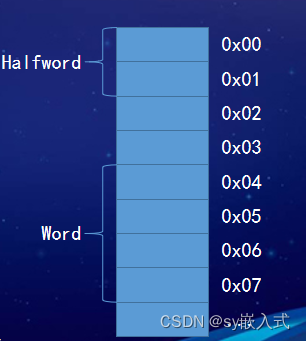

5.ARM数据类型

ARM采用32位架构,基本数据类型有以下三种

Byte 8bits 字节

Halfword 16bits 半字

Word 32bits 全字

DoubleWord 64bits 两字

数据存储

Word型数据在内存的起始地址必须是4的整数倍

Halfword型数据在内存的起始地址必须是2的整数倍

注:即数据本身是多少位在内存存储时就应该多少位对齐 字节对齐原则

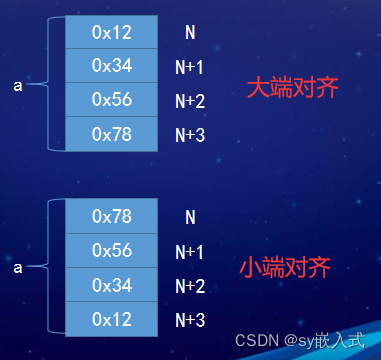

字节序

大端对齐

低地址存放高位,高地址存放低位

a = 0x12345678;

小端对齐

低地址存放低位,高地址存放高位

a = 0x12345678; 注:ARM一般使用小端对齐

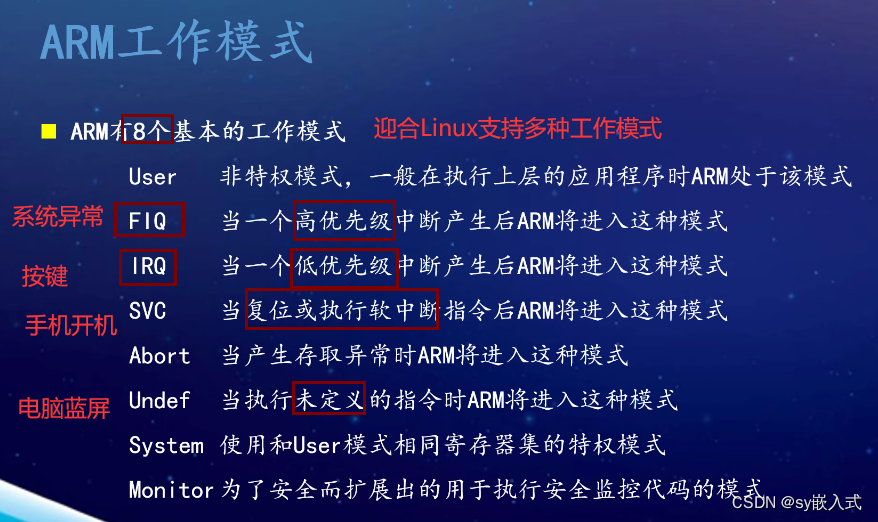

6.ARM工作模式

不同模式拥有不同权限

不同模式执行不同代码

不同模式完成不同的功能

1.ARM工作模式分类

按照权限

User为非特权模式(权限较低),其余模式均为特权模式(权限较高)

按照状态

FIQ、IRQ、SVC、Abort、Undef属于异常模式,即当处理器遇到异常后 会进入对应的模式

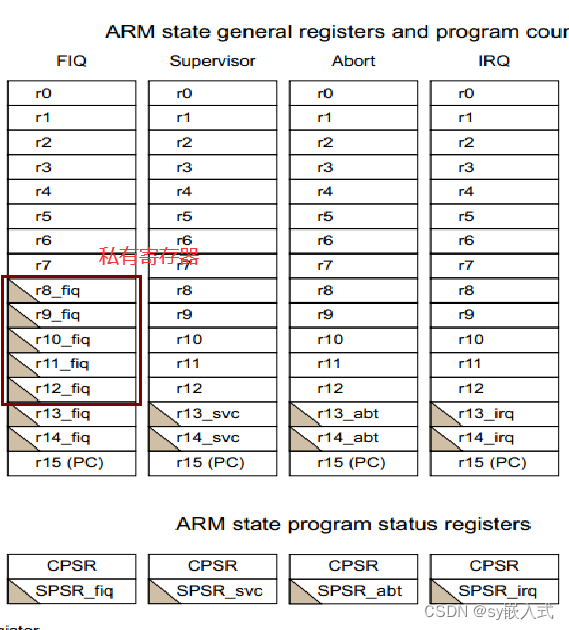

7.寄存器

概念 寄存器是处理器内部的存储器,没有地址

作用 一般用于暂时存放参与运算的数据和运算结果

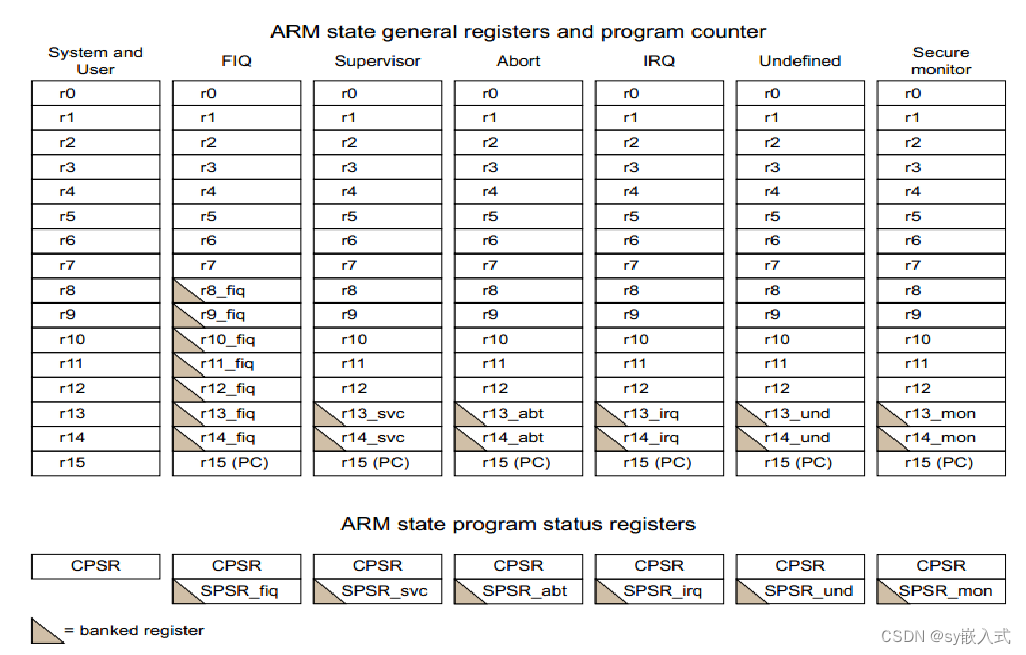

分类 包括通用寄存器(R0-R12)、专用寄存器(R13-R15)、控制寄存器

注:在某个特定模式下只能使用当前模式下的寄存器,一个模式下特有的寄存器其他模式下不可使用

1.专用寄存器

R15(PC,Program Counter)

程序计数器,用于存储当前取址指令的地址

R14(LR,Link Register)

链接寄存器,一般有以下两种用途:

> 执行跳转指令(BL/BLX)时,LR会自动保存跳转指令下一条指令的地址

程序需要返回时将LR的值复制到PC即可实现

> 产生异常时,对应异常模式下的LR会自动保存被异常打断的指令的下

一条指令的地址,异常处理结束后将LR的值复制到PC可实现程序返回

R13(SP,Stack Pointer)

栈指针,用于存储当前模式下的栈顶地址

2.CPSR寄存器

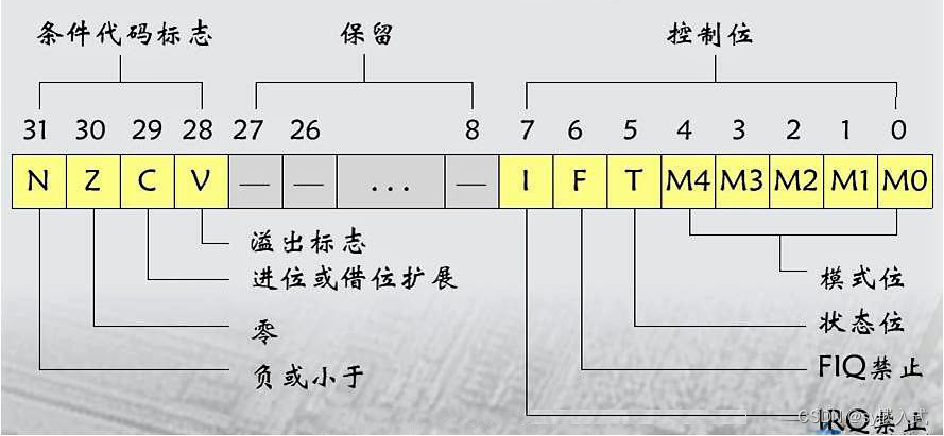

CPSR(Current Program Status Register),当前程序状态寄存器

CPSR寄存器分为四个域,[31:24]为条件域用F表示、[23:16]为状态域用S表示、[15:8]为预留域用X表示、[8:0]为控制域用C表示。

模式位:切换ARM工作模式;状态位:一般为ARM状态

- Bit[4:0] [10000]User [10001]FIQ [10010]IRQ [10011]SVC [10111]Abort [11011]Undef [11111]System [10110]Monitor

- Bit[5] [0]ARM状态 [1]Thumb状态

- Bit[6] [0]开启FIQ [1]禁止FIQ

- Bit[7] [0]开启IRQ [1]禁止IRQ

Bit[28] V 溢出标志

> 当运算器中进行加法运算且产生符号位进位时该位自动置1,否则为0

> 当运算器中进行减法运算且产生符号位借位时该位自动置0,否则为1

Bit[29] C 进位或借位扩展

> 当运算器中进行加法运算且产生进位时该位自动置1,否则为0

> 当运算器中进行减法运算且产生借位时该位自动置0,否则为1

Bit[30] Z 零

当运算器中产生了0的结果该位自动置1,否则为0

Bit[31] N 负数

当运算器中产生了负数的结果该位自动置1,否则为0

二、ARM异常处理

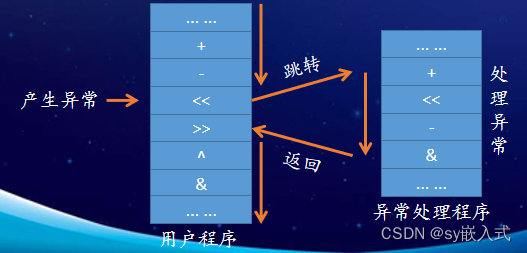

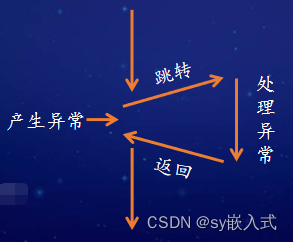

1.异常

概念

处理器在正常执行程序的过程中可能会遇到一些不正常的事件发生,这时处理器就要将当前的程序暂停下来转而去处理这个异常的事件,异常事件处理完成之后再返回到被异常打断的点继续执行程序

异常处理机制

不同的处理器对异常的处理的流程大体相似,但是不同的处理器在具体实现的机制上有所不同;比如处理器遇到哪些事件认为是异常事件遇到异常事件之后处理器有哪些动作、处理器如何跳转到异常处理程序如何处理异常、处理完异常之后又如何返回到被打断的程序继续执行等我们将这些细节的实现称为处理器的异常处理机制

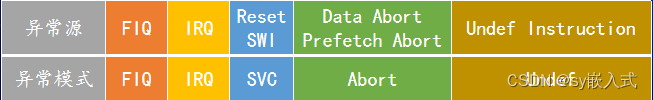

2.ARM异常源

概念

导致异常产生的事件称为异常源

ARM异常源(触发中断的方式)

FIQ 快速中断请求引脚有效

IRQ 外部中断请求引脚有效

Reset 复位电平有效

Software Interrupt 执行swi指令 (软中断)

Data Abort 数据终止

Prefetch Abort 指令预取终止

Undefined Instruction 遇到不能处理的指令

3.ARM异常模式

在ARM的基本工作模式中有5个属于异常模式,即ARM遇到异常后会切换成对应的异常模式

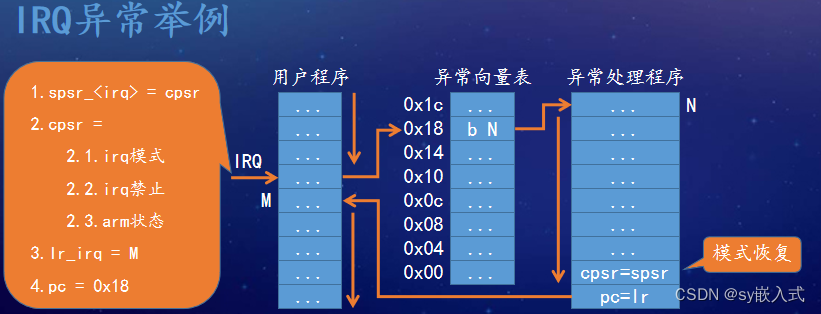

4.ARM异常响应

ARM产生异常后的动作(自动完成)

1.拷贝CPSR中的内容到对应异常模式下的SPSR_<mode> --备份

2.修改CPSR的值(状态寄存器)

2.1.修改中断禁止位禁止相应的中断 --没有NVIC,不支持中断嵌套

2.2.修改模式位进入相应的异常模式

2.3.修改状态位进入ARM状态

3.保存返回地址到对应异常模式下的LR_<mode>

4.设置PC为相应的异常向量(异常向量表对应的地址)

5.异常向量表

异常向量表

> 异常向量表的本质是内存中的一段代码

> 表中为每个异常源分配了四个字节(32位)的存储空间

> 遇到异常后处理器自动将PC修改为对应的地址

> 因为异常向量表空间有限一般我们不会再这里写异常处理程序,而是在对应的位置写一条跳转指令使其跳转到指定的异常处理程序的入口

注:ARM的异常向量表的基地址默认在0x00地址(复位),但可以通过配置协处理器来修改其地址

6.异常返回

ARM异常返回的动作(自己编写)

1.将SPSR_<mode>的值复制给CPSR,使处理器恢复之前的状态

2.将LR_<mode>的值复制给PC,使程序跳转回被打断的地址继续执行

注:整个过程CPSR保存的永远是当前程序运行状态,SPSR只是异常时对原来的CPSR进行备份

7.异常优先级

多个异常同时产生时的服务顺序

Reset > Data Abort > FIQ > IRQ >Prefetch Abort > Software Interrupt > Undefined instruction

FIQ的响应速度比IRQ快

1. FIQ在异常向量表位于最末,可直接把异常处理写在异常向量表之后,省去跳转

2. FIQ模式有5个私有寄存器(R8-R12),执行中断处理程序前无需压栈保存寄存器,可直接处理中断

3. FIQ的优先级高于IRQ

3.1 两个中断同时发生时先响应FIQ

3.2 FIQ可以打断IRQ,但IRQ不能打断FIQ

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结