您现在的位置是:首页 >技术交流 >[FPGA/VerilogHDL/Xilinx]设计约束之时序约束(二)网站首页技术交流

[FPGA/VerilogHDL/Xilinx]设计约束之时序约束(二)

约束输入和输出端口

除了指定设计的每个端口的位置和 I/O 标准外,还必须指定输入和输出延迟约束以描述进出器件接口的外部路径的时序。这些延迟是根据通常同样在开发板上生成并进入器件的时钟来定义的。在某些情况下,如果与 I/O 路径相关的时钟所含波形不同于开发板时钟的波形,那么必须根据虚拟时钟来定义延迟。

我们在<设计约束之时序约束(一)>分析内部路径时,建立和保持分析都会考虑最小和最大延迟。对于I/O 路径而言同样如此。基于这个原因,对最小和最大延迟条件进行描述就显得尤为重要。默认情况下 I/O 时序路径可作为单周期路径进行分析,这意味着:

-

为实现最大延迟分析(建立),数据的捕获比单倍数据速率接口的发送沿晚 1 个时钟周期,比双倍数据速率接口的发送沿晚半个时钟周期。

-

为实现最小延迟分析(保持),请在相同时钟沿发送和捕获数据。

如果时钟和 I/O 数据之间的关系必须以不同方式进行时序约束(例如在时钟源同步接口中),那么必须指定不同的 I/O延迟和附加时序例外。这对应于高级 I/O 时序约束方案。

定义输入延迟

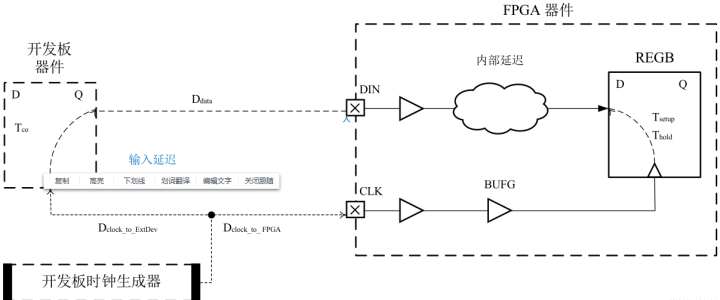

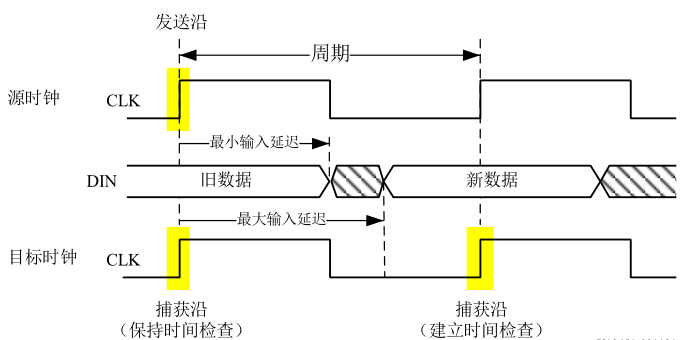

输入延迟定义为与器件接口处的时钟相关的延迟。除非已在参考时钟的源管脚上指定 set_clock_latency,否则输入延迟对应于从发送沿到时钟走线、外部器件和数据走线的绝对时间。如果已单独指定时钟时延,即可忽略时钟走线延迟。

输入延时计算

两类分析的输入延迟数值:

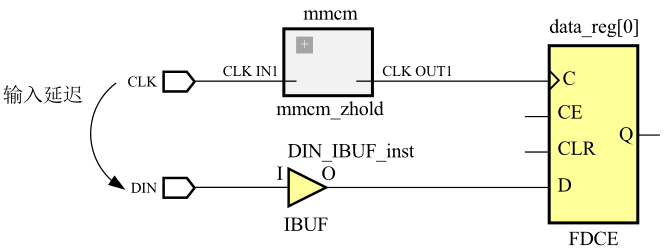

Input Delay(max) = Tco(max) + Ddata(max) + Dclock_to_ExtDev(max) - Dclock_to_FPGA(min) Input Delay(min) = Tco(min) + Ddata(min) + Dclock_to_ExtDev(min) - Dclock_to_FPGA(max)下图显示了建立时间(最大值)和保持时间(最小值)分析的输入延迟约束的简单示例,其中假定已在 CLK 端口上定义 sysClk 时钟:

set_input_delay -max -clock sysClk 5.4 [get_ports DIN] set_input_delay -min -clock sysClk 2.1 [get_ports DIN]输入延迟为负表示数据到达器件接口的时间早于发送时钟沿。

解读最小和最大输入延迟

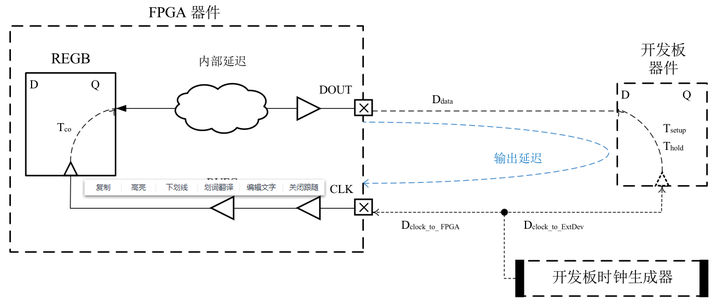

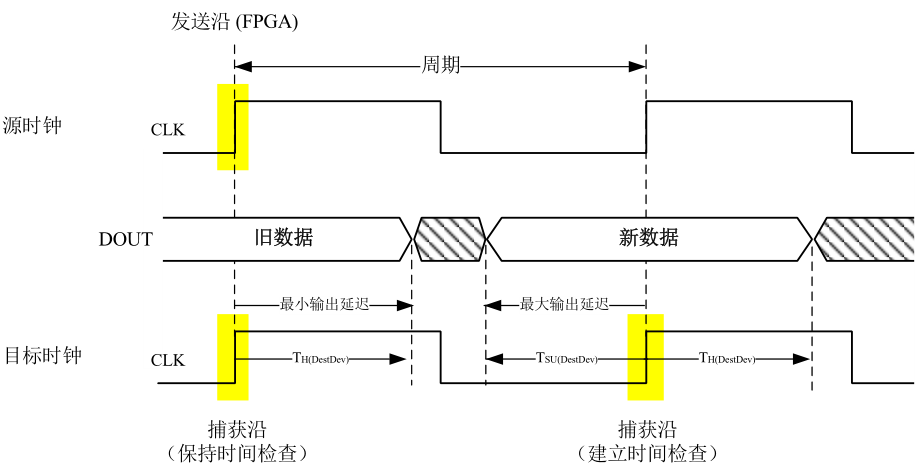

定义输出延迟

输出延迟与输入延迟类似,区别在于输出延迟表示为了确保在所有情况下均可正常工作,输出路径在器件外部的最短和最长时间。

输出延迟计算

两类分析的输出延迟数值:

Output Delay(max) = Tsetup + Ddata(max) + Dclock_to_FPGA(max) - Dclock_to_ExtDev(min) Output Delay(min) = Ddata(min) - Thold + Dclock_to_FPGA(min) - Dclock_to_ExtDev(max)

下图显示了建立时间(最大值)和保持时间(最小值)分析的输出延迟约束的简单示例,其中假定在 CLK 端口上已定义 sysClk 时钟:

set_output_delay -max -clock sysClk 2.4 [get_ports DOUT] set_output_delay -min -clock sysClk -1.1 [get_ports DOUT]输出延迟对应于开发板上捕获沿之前的延迟。对于其中时钟和数据开发板走线已实现平衡的常规系统同步接口而言,目标器件的建立时间用于定义输出延迟最大值分析。目标器件保持时间用于定义输出延迟最小值分析。指定的输出延迟最小值表示从设计发出信号开始到在目标器件接口上使用信号进行保持时间分析之前,所发生的最小延迟。因此,块内部的延迟可小得多。输出延迟最小值为正值表示信号在设计内部可能具有负延迟。因此,输出延迟最小值通常为负值。例如,以下代码示例表示设计内部截至 DOUT 为止的延迟必须至少为 +0.5 ns 才能满足保持时间要求。

set_output_delay -min -0.5 -clock CLK [get_ports DOUT]

解读最小和最大输出延迟

选择参考时钟

报告进出端口的时序

无论端口是否已约束,均可使用 report_timing 命令识别设计中端口的相关时钟。定义完所有时序时钟后,即可报告进出 I/O 端口的最差路径、创建与报告的时钟相关的 I/O 延迟约束,并为进出设计的其它时钟重新运行相同的时序报告。如果发现端口与多个时钟相关,请创建对应的约束并重复此过程。

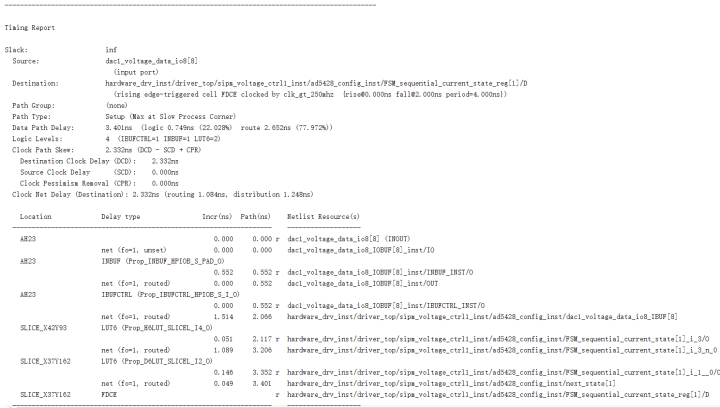

report_timing -from [get_ports din] -sort_by group 示例:report_timing -from [get_ports dac1_voltage_data_io8[8]] -sort_by group该TCL指令不仅可用于报告当前端口的相关时钟,也可用作由IO输入逻辑的时序路径的分析,在下图的报告中可以看到,该条路径的延时数据、逻辑级数以及各级逻辑级数带来的延时均可呈现。

另外,还可使用“时序汇总 (Timing Summary)”报告并选中 -report_unconstrained 选项来运行同样的分析。

使用基准时钟

基准时钟(即传入开发板时钟)应在以下情况下使用:当它直接控制 I/O 路径时序单元,而不遍历任何时钟修改块时。I/O 延迟线不能视作为时钟修改块,因为这些延迟线仅影响时钟插入延迟,不影响波形。大多数情况下,外部器件的接口特性是根据相同开发板时钟定义的。当以采用零保持时间违例 (ZHOLD) 模式的器件内的 PLL 或 MMCM 补偿基准时钟时,I/O 路径时序单元连接到基准时钟的内部副本(例如,生成时钟)。由于两个时钟的波形完全相同,Xilinx建议使用基准时钟作为输入/输出延迟约束的参考时钟。

使用虚拟时钟

当板载时钟遍历某一时钟修改块以对波形进行变换并补偿整体插入延迟时,建议使用虚拟时钟代替开发板时钟作为输入和输出延迟的参考时钟。虚拟时钟的使用场景主要有以下 3 种:

-

内部时钟与板载时钟具有不同周期:虚拟时钟必须定义为:具有与内部时钟相同的周期和波形。其结果是要求 I/O路径为常规的单周期路径,

-

对于输入路径来说,内部时钟相比于板载时钟拥有正向移位波形:虚拟时钟的定义类似板载时钟,针对建立时间定义一条从虚拟时钟到内部时钟的多周期路径(双周期)约束。上述约束导致强制执行建立时间时序分析,并且分析要求为 1 个时钟周期加相位移动量。

-

对于输出路径来说,内部时钟相比于板载时钟拥有负向移位波形:虚拟时钟的定义类似板载时钟,针对建立时间定义一条从内部时钟到虚拟时钟的多周期路径(双周期)约束。上述约束导致强制执行建立时间时序分析,并且分析要求为 1 个时钟周期加相位移动量。

使用生成时钟

对于输出源同步接口,设计会生成 1 个内部时钟的副本并将其随同数据转发送给开发板。如需控制并报告转发时钟与数据之间的相位关系(偏差),即可使用此时钟作为输出数据延迟约束的参考时钟。转发时钟同样能用于系统同步接口的输入与输出延迟约束。

参考时钟上升沿和下降沿

I/O 约束使用的时钟沿必须与连接到器件的外部器件的数据手册一致。默认情况下,set_input_delay 和set_output_delay 命令定义 1 个相对于参考时钟上升沿的延迟约束。大多数情况下,I/O 参考时钟沿对应于用来锁存或发送器件内 I/O 数据的时钟沿。通过分析 I/O 时序路径,可复查已使用的时钟沿,并核实这些时钟沿与其实际硬件行为是否对应。对于仅与时钟下降沿内部相关的 I/O 路径而言,如果误将时钟上升沿用作为此类路径的参考时钟,那么路径要求为 ½ 周期,这会导致时序收敛更加困难。

验证延迟约束

输入 I/O 时序约束后,复查 I/O 路径上的时序分析方式以及建立时间和保持时间检查的裕量违例数量就显得至关重要。通过使用进出所有端口的时序报告进行建立时间和保持时间分析(即,delay type = min_max)即可验证:

-

• 是否已将正确的时钟和时钟沿用作延迟约束的参考。

-

• 是否已使用预期时钟来发送和捕获器件内部的 I/O 数据。

-

• 是否能通过布局或设置适当的延迟界限配置以合理方式修复违例。如果无法修复,则必须复查约束中输入的 I/O 延迟值,并评估其合理性,以及是否需要修改设计以满足时序要求。

I/O 路径报告命令行示例

report_timing -from [all_inputs] -nworst 1000 -sort_by group -delay_type min_max report_timing -to [all_outputs] -nworst 1000 -sort_by group -delay_type min_maxI/O 延迟约束错误会导致无法实现时序收敛。实现工具由时序驱动并且致力于对布局布线进行最优化以满足时序要求。如果 I/O 路径要求无法得到满足,并且 I/O 路径在设计中发生最严重的违例,那么总体设计 QoR 将受到影响。

输入至输出馈通路径

有多种用来约束输入端口到输出端口间组合路径的等效方法。

示例 1:使用周期大于或等于馈通路径的目标最大延迟的虚拟时钟,并按如下方式应用最大输入和输出延迟约束.

create_clock -name vclk -period 10 set_input_delay -clock vclk <input_delay_val> [get_ports din] -max set_output_delay -clock vclk <output_delay_val> [get_ports dout] -max其中,本例仅约束最大延迟。

input_delay_val(max) + feedthrough path delay (max) + output_delay_val(max) <= vclk period.示例 2:在馈通端口之间使用最小延迟与最大延迟约束组合。

set_max_delay -from [get_ports din] -to [get_ports dout] 10 set_min_delay -from [get_ports din] -to [get_ports dout] 2这是同时约束路径上的最小延迟和最大延迟的简单方法。时序分析期间将同时使用相同端口上的所有现有输入和输出延迟约束。因此,这种方法并不常用。最大延迟通常针对“慢速时序角点 (Slow Timing Corner)”进行最优化和报告,而最小延迟则发生在“Fast Timing Corner”中。最好对馈通路径延迟约束运行几次迭代,以验证其合理性并确保实现工具可满足这些约束要求,当布局的端口间距离相去较远时尤其如此。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结