您现在的位置是:首页 >学无止境 >[FPGA/VerilogHDL/Xilinx]Aurora接口及协议网站首页学无止境

[FPGA/VerilogHDL/Xilinx]Aurora接口及协议

简介[FPGA/VerilogHDL/Xilinx]Aurora接口及协议

1.概述

Aurora 协议是一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议,并

为物理层提供透明接口,让专有协议或业界标准协议上层能方便地使用高速收发器

Aurora协议在Xilinx的FPGA上有两种实现方式:8B/10B与64B/10B。两个协议大部分相同,主要区别在编码方式上:

-

Aurora-8B/10B:将8bit数据编码成10bit数码进行传输,尽量平衡数据中“0”和“1”的个数以实现DC平衡,显然这个编码方式的开销是20%,也就是效率为80%

-

Aurora-64B/10B:将64bit数据编码成66bit块传输,66bit块的前两位表示同步头,主要由于接收端的数据对齐和接收数据位流的同步。同步头有“01”和“10”两种,“01“表示后面的64bit都是数据,“10”表示后面的64bit是数据信息。数据信息0和1不一定是平衡的,因此需要进行加扰,开销较小。

Aurora-8B/10B

常用于芯片(FPGA)与芯片(FPGA)之间通信。它用于使用一个或多个收发器在设备之间传输数据。它具备以下特征:

-

作为通用数据通道,它的数据吞吐范围为 480Mb/s~84.48Gb/s;

-

支持多达16个连续键合的7系列GTX/GTH、UltraScaleGTH或UltraScale+GTH收发器和多达4个键合GTP收发器;

-

Aurora-8B/ 10B 符合协议规范v2.3;

-

资源占用低;

-

Aurora-IP 基于AXI-Streaming的数据接口以及控制接口实现,方便使用;

-

通道初始化及通信过程中的通道维持自动实现;

-

支持全双工、单工通信;

-

16位加扰器/解扰器;

-

用于用户数据的16位或32位循环冗余校验(CRC);

-

热插拔逻辑;

-

可配置的DRP/INIT时钟;

-

GTREFCLK和内核INIT_CLK的单/差分时钟选项。

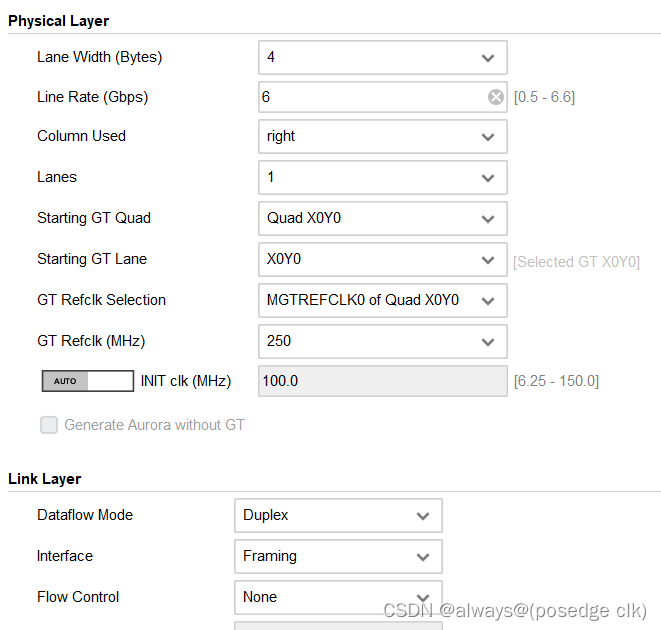

2.Aurora-8B/10B IP

Xilinx提供的

Aurora-8B/10B IP

是一个可扩展的,轻量级的,用于高速串行通信的链路层协议。

该协议是开放的,可以使用赛灵思FPGA技术实现。该协议通常用于需要简单、低成本、高速率数据通道的应用中,并用于使用一个或多个收发器在设备之间传输数据。

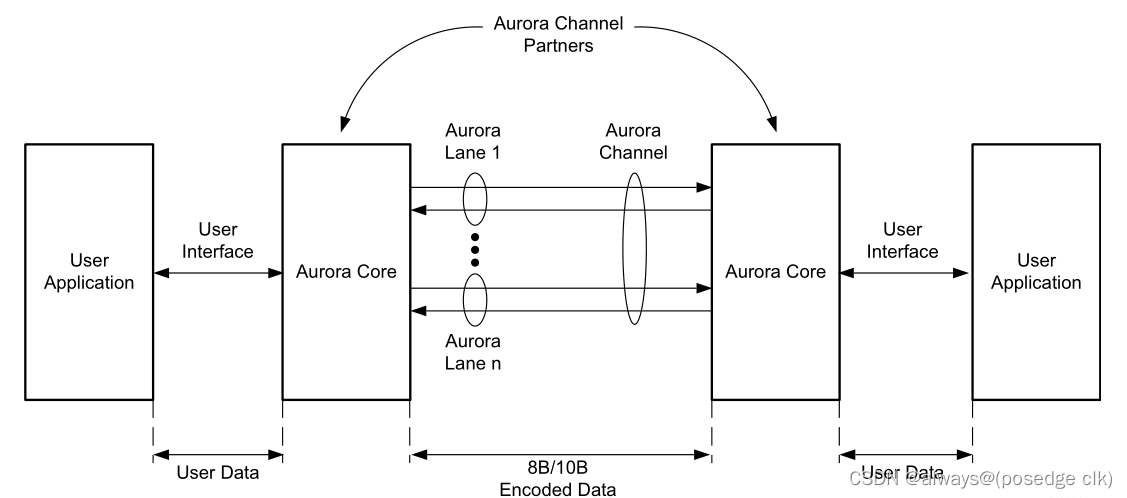

Aurora 8B/10B数据通道

Aurora8B/10B内核的主要功能模块有:

-

Lane Logic(通道逻辑):每个GTP、GTX 或GTH收发器(以下称为收发器)由通道逻辑模块的实例驱动,它初始化每个单独的收发器并处理编码以及控制字符的解码和错误检测。

-

Global Logic(全局逻辑):全局逻辑模块执行通道初始化的绑定和验证阶段。在运行过程中,模块会生成Aurora协议所需的随机空闲字符,并监控所有通道逻辑模块的错误。

-

RX User Interface(RX 用户接口):AXI4-Stream RX用户接口将数据从通道移动到应用程序并执行流量控制功能。

-

TX User Interface(TX 用户接口):AXI4-Stream TX用户接口将数据从应用程序移动到通道并执行流量控制TX功能。标准时钟补偿模块嵌入内核中。该模块控制时钟补偿 (CC) 字符的周期性传输。

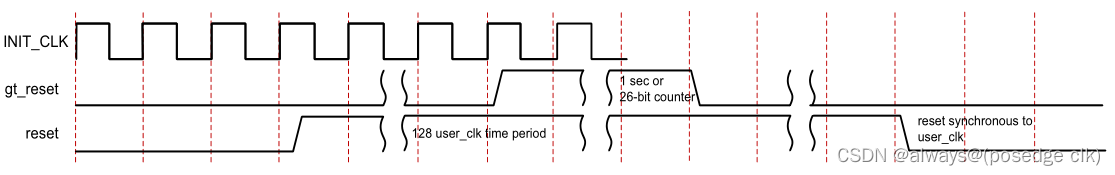

2.1 控制信号接口及时序

-

INIT_CLK:初始化时钟,基于 Aurora IP进行配置,应低于RefCLK.

-

REF_CLK:GTH参考时钟,应使用SERDES所在BANK输入的同步时钟,使用经由IBUFDS的O端口输出信号作为RefCLK,基于Aurora IP进行配置为实际频率。

-

USER_CLK/SYNC_CLK:用户时钟,计算方法:LineRate×(8/10)/LaneWide(bit) = clk_freq(Ghz),例如6Gbps×(8/10)/32bit = 0.15Ghz = 150Mhz。

-

gt_reset:与INIT_CLK同步,是对底层GTH的复位,复位的级别高于 reset,类似硬件复位。gt_reset经过防抖处理会后 连接到顶层,应当在硬件模块第一次上电时拉高,至少保持6个时钟周期,该操作会重置收发器的所有物理编码子层(PCS)和物理介质附件(PMA)子组件。

-

reset: 与USER_CLK同步,是对Aurora IP的复位,类似软件复位。reset 至少保持6个时钟周期。

复位控制时序

-

CORE_CONTROL_loopback( 回环模式 ):000:normal; 001: Near-end PCS Loopback ;010: Near-end PMA Loopback; 100: Far-end PMA Loopback; 110: Far-end PCS Loopback。

-

CORE_CONTROL_pll_not_locked:连接(~pll_locked);

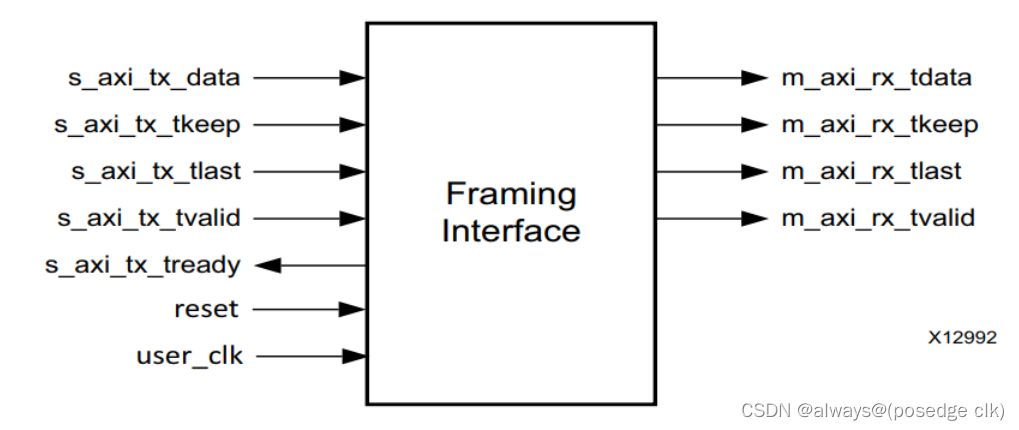

2.2 数据交互接口及时序

接口示意图如下图所示:

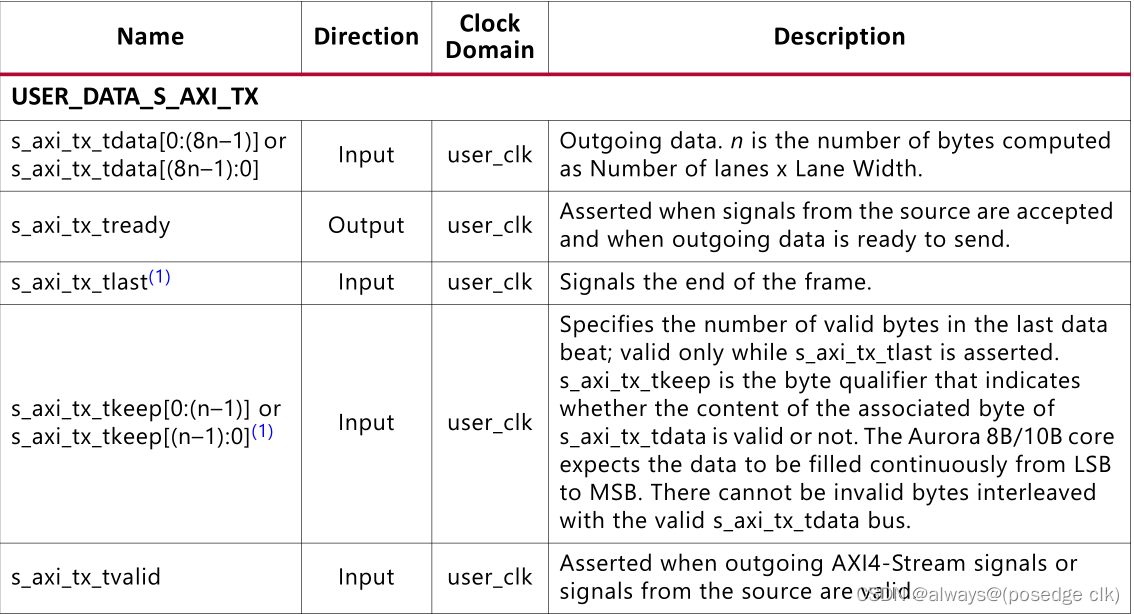

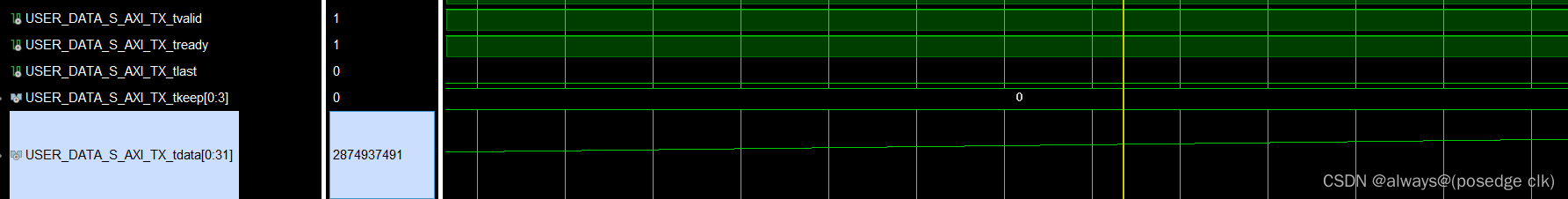

数据发送端口定义如下图所示:

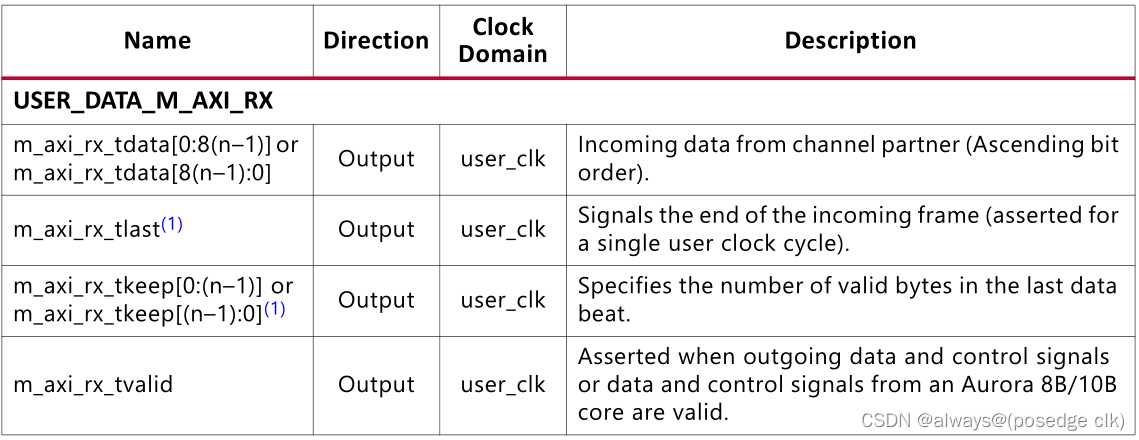

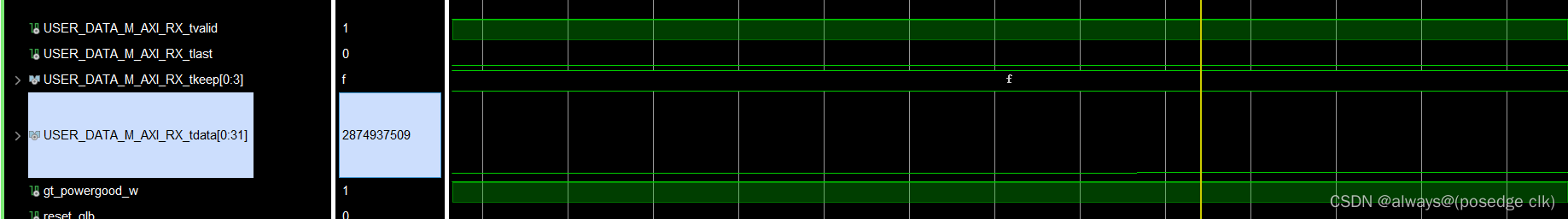

数据发送接收定义如下图所示:

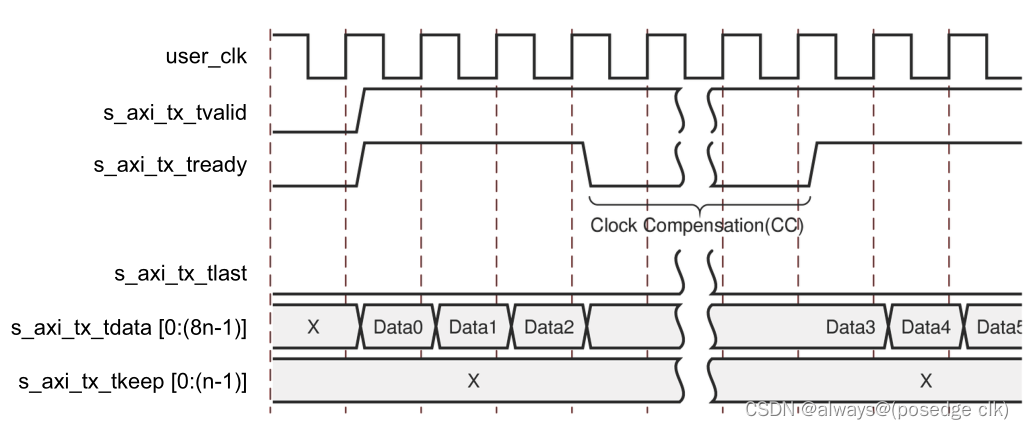

数据发送时序如下图所示:

-

当s_axi_tx_tready与s_axi_tx_tvalid握手成功后,即可发送数据;

-

使用s_axi_tx_tlast来表示当前发送最后一个数据;

-

s_axi_tx_tkeep来表示最后一个数据的有效字节(应用场景在发送奇数个字节时,IP核会自动添加一个pad到数据中,所以存在一个无效字节需要指出)。

数据接收时序如下图所示:

-

接收数据不需要握手过程;

-

当m_axi_rx_tvalid为高时,即说明此时的数据是有效数据;

-

m_axi_rx_tkeep与m_axi_rx_tlast的用法与发送端对应的信号一致。

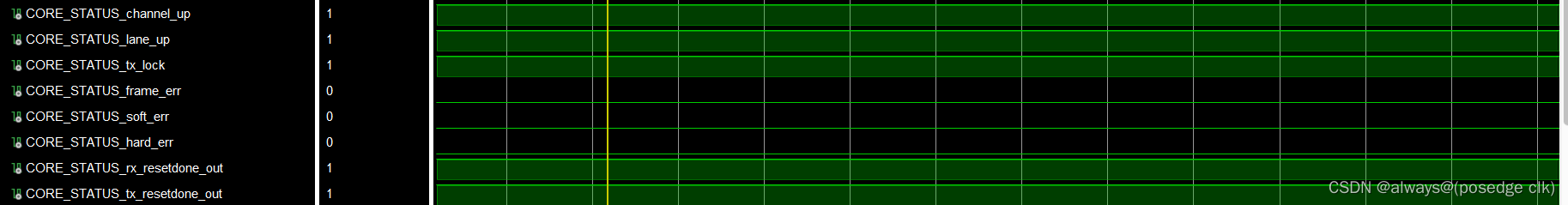

2.3 状态监测接口及时序

-

channel_up:“ 1”状态指示 通道初始化完成,通道已准备好进行数据传输。

-

lane_up: “ 1”状态指示 个通道初始化成功,每个位代表一个通道;

-

frame_err:当前通道帧协议错误;

-

hard_err:硬件错误指示;

-

soft_err:软件错误指示;

3.详细设计

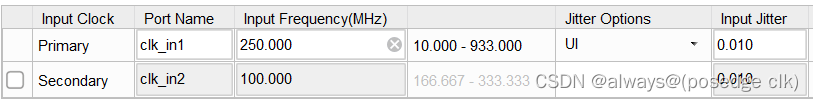

3.1 时钟设计:

输入时钟:

//SerDes interface

input gth_clk_n_i,

input gth_clk_p_i,

差分时钟处理:

IBUFDS_GTE4 IBUFDS_GTE4

(

.I (gth_clk_p_i),

.IB (gth_clk_n_i),

.CEB (1'b0),

.O (gth_clk),//TO SERDES REF CLK 250MHZ

.ODIV2 (gth_clk_i)//TO BUFG 250MHZ

);

BUFG_GT BUFG_GT (

.CE (1'b1),

.CEMASK (1'b1),

.CLR (1'b0),

.CLRMASK (1'b1),

.DIV (3'b000),

.I (gth_clk_i),

.O (gth_clk_w)//TO PLL INPUT 250MHZ

);

PLL设计:

3.2 Aurora IP:

3.3 驱动

复位信号:

/

reg gt_reset ;

reg[9:0]gt_reset_cnt;

/

always@(posedge init_clk or posedge reset)

begin

if(reset)

begin

gt_reset <= 'd1 ;

gt_reset_cnt <= 0 ;

end

else if(gt_reset_cnt[9] == 1)

begin

gt_reset <= 'd0 ;

gt_reset_cnt <= gt_reset_cnt ;

end

else

begin

gt_reset <= 'd1 ;

gt_reset_cnt <= gt_reset_cnt + 1 ;

end

end

/

reg [7:0]reset_cdc;

reg gt_reset_done;

/

always@(posedge user_clk or posedge reset)

begin

if(reset)

begin

reset_cdc <= 'd0 ;

end

else

begin

reset_cdc <= {reset_cdc[6:0],gt_reset_cnt[9]} ;

end

end

always@(posedge user_clk or posedge reset)

begin

if(reset)

begin

gt_reset_done <= 1'd0 ;

end

else if(reset_cdc[6]&&~reset_cdc[7])

begin

gt_reset_done <= 1'd1 ;

end

else ;

end

/

控制信号:

/

//control

wire [2:0]CORE_CONTROL_loopback;

assign CORE_CONTROL_loopback = 3'b010 ;

//LOOPBACK MODE:

//001: Near-end PCS Loopback

//010: Near-end PMA Loopback

//100: Far-end PMA Loopback

//110: Far-end PCS Loopback

wire CORE_CONTROL_pll_not_locked;

assign CORE_CONTROL_pll_not_locked = ~pll_locked ;

wire CORE_CONTROL_power_down;

assign CORE_CONTROL_power_down = 1'b0 ;

/

4.设计验证

4.1状态监测

4.2数据发送

4.3数据接收

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结