您现在的位置是:首页 >技术教程 >CCFC22102B 时钟分析网站首页技术教程

CCFC22102B 时钟分析

简介CCFC22102B 时钟分析

CCFC2012BC基于国芯科技自主PowerPC架构C*Core CPU内核研发,是一款汽车电子中高端车身及网关控制芯片,可广泛应用于车身控制和网关以及新能源车的整车控制,实现对国外产品如NXP(恩智浦)MPC5604BC、MPC5607B系列以及ST的SPC560B50、SPC560B64系列相应产品的替代

时钟体系

系统时钟三种来源:

其他的低速时钟源:

时钟体系图:

其中peripheral set (1, 2 or 3)是由系统时钟分频或倍频得到,peripheral set (1, 2 or 3)分别给不同的外设:

FMPLL时钟配置

CCFC22102B选用FMPLL作为系统时钟,FMPLL时钟频率的配置。

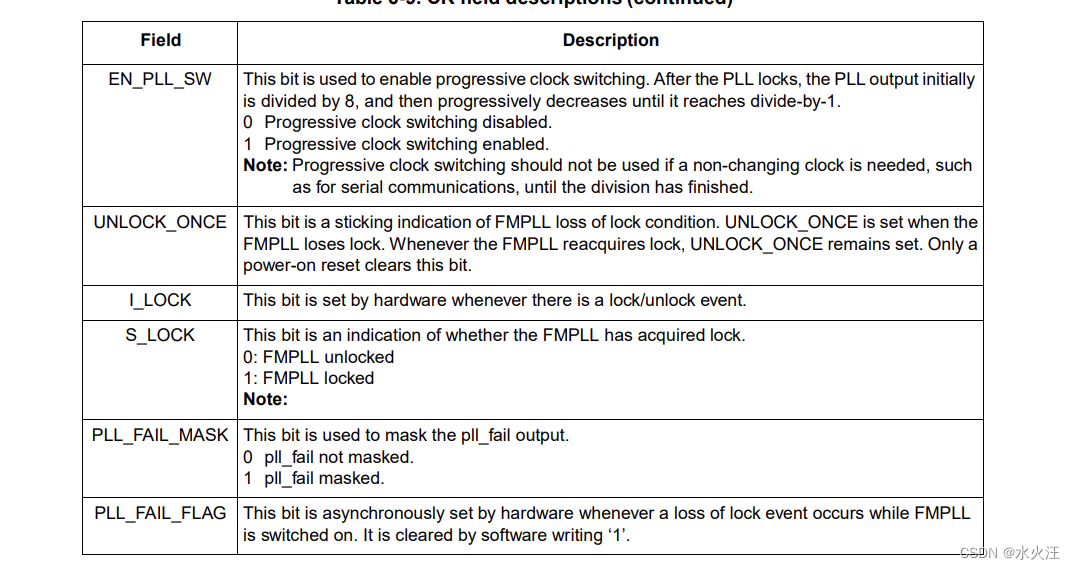

上面是将FXOSC作为FMPLL的输入时钟源,经过设置VCO、ODF、NDIV的值来配置FMPLL时钟,CCFC22102B的FMPLL为64mhz。

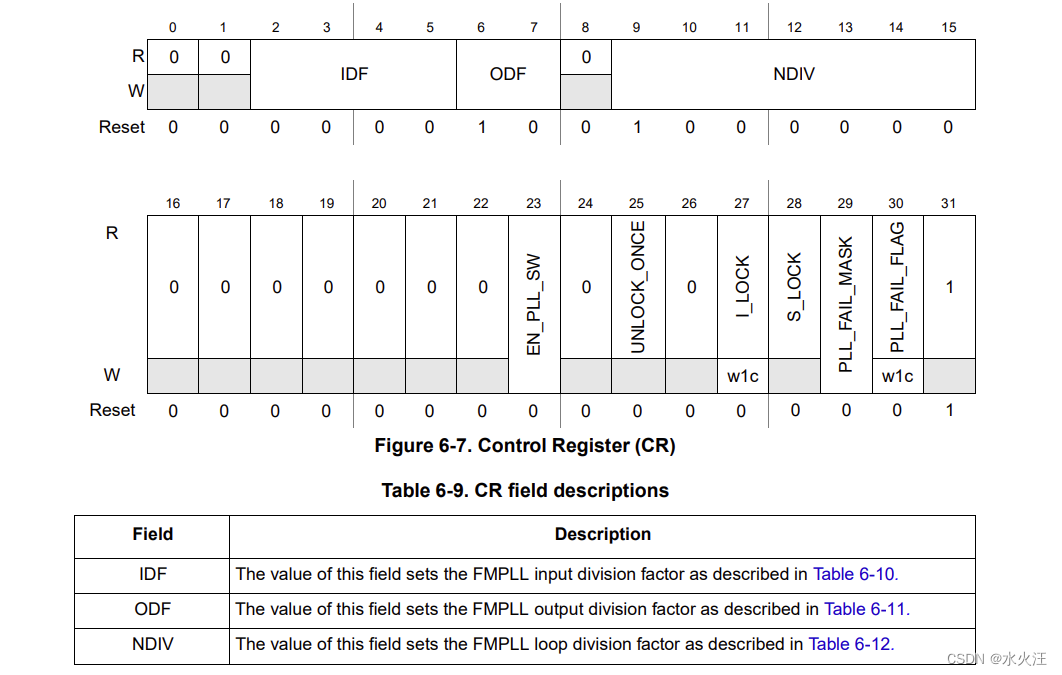

寄存器配置信息:

代码操作:

/*phi=(clkin*NDIV)/(IDF*ODF)=(16*32)/(2*4)=64MHz*/

CGM.FMPLL_CR.R = 0x05200100u;FMPLL配置为系统时钟

当 CCFC22102B运行在RUN0时,配置如下寄存器,将FMPLL配置为系统时钟,此时系统时钟为64MHZ;

union { /* RUN 0->4 Mode Configuration (+0x0030-0x003C) */

vuint32_t R;

struct {

vuint32_t :8;

vuint32_t PDO:1;

vuint32_t :2;

vuint32_t MVRON:1;

vuint32_t DFLAON:2;

vuint32_t CFLAON:2;

vuint32_t :9;

vuint32_t FMPLLON:1;

vuint32_t FXOSCON:1;

vuint32_t FIRCON:1;

vuint32_t SYSCLK:4;

} B;

} RUN[4];

/* RUN0 cfg: 16MHzIRCON,OSC0ON,PLL0ON,syclk=PLL0 */

ME.RUN[0].R = 0x001F0074u;后4位4为:对应0100:

外设时钟的配置

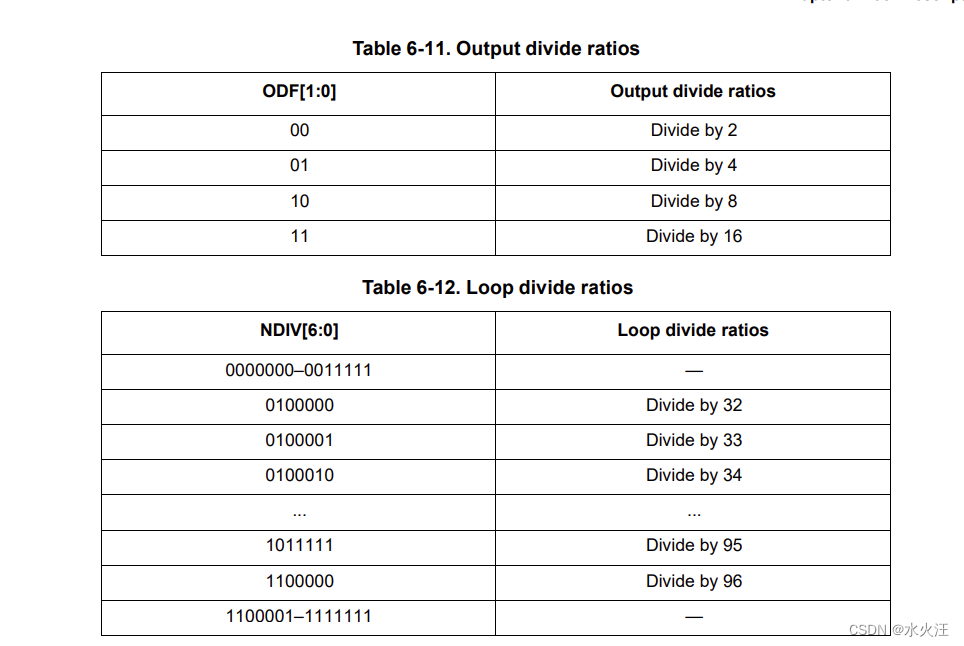

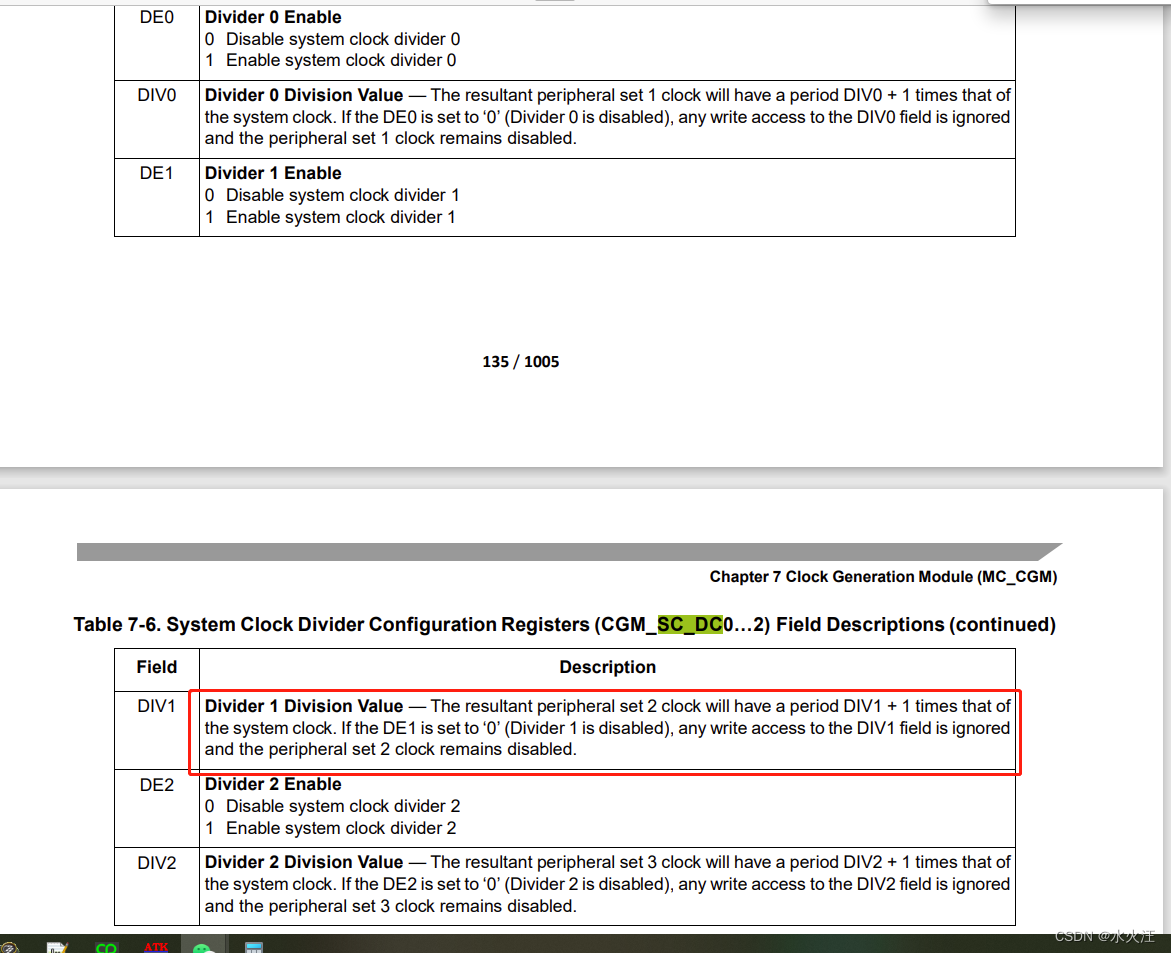

在CGM_SC_DC0进行配置:

CGM.SC_DC[0].R = 0x80u; /* Enable system clock divider 0 */

CGM.SC_DC[1].R = 0x83u; /* Enable system clock divider 1 */

CGM.SC_DC[2].R = 0x80u; /* Enable system clock divider 2 */所以peripheral set 0被配置为64mhz,peripheral set 1被配置为16mzh,peripheral set 2被配置为64mhz。

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结