您现在的位置是:首页 >其他 >09 FPGA—利用状态机实现可乐售卖机(附代码)网站首页其他

09 FPGA—利用状态机实现可乐售卖机(附代码)

简介09 FPGA—利用状态机实现可乐售卖机(附代码)

1. 理论

FPGA 是并行执行的,如果我们想要处理具有前后顺序的事件,就需要引入状态机。举个例子,将人看成 FPGA ,我们可以在散步的时候听歌和聊天这是并行执行的,但一天的行程安排却是以时间段前后执行的。

状态机简写为 FSM( Finite State Machine),称为同步有限状态机,简称为状态机,之所以说“同步”是因为状态机中所有的状态跳转都是在时钟的作用下进行的,而“有限”则是说状态的个数是有限的。状态机根据影响输出的原因分为两大类,即Moore 型状态机和 Mealy 型状态机,其共同点是:状态的跳转都只和输入有关。区别主要是在输出的时候:若最后的输出只和当前状态有关而与输入无关则称为 Moore 型状态机;若最后的输出不仅和当前状态有关还和输入有关则称为 Mealy 型状态机(使用较多)。

状态机的每一个状态代表一个事件,从执行当前事件到执行另一事件我们称之为状态的跳转或状态的转移,我们需要做的就是执行该事件然后跳转到一下事件。

2. 实操

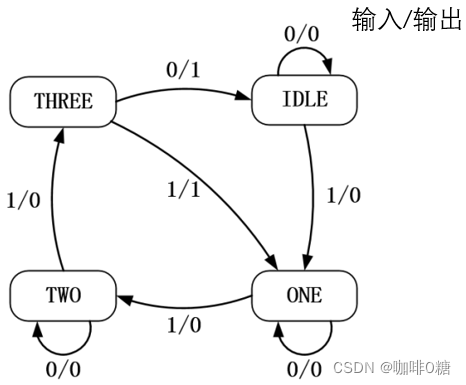

实验目标:可乐机每次只能投入 1 枚 1 元硬币,且每瓶可乐卖 3 元钱,即投入 3 个硬币就可以让可乐机出可乐,如果投币不够 3 元想放弃投币需要按复位键,否则之前投入的钱不能退回。

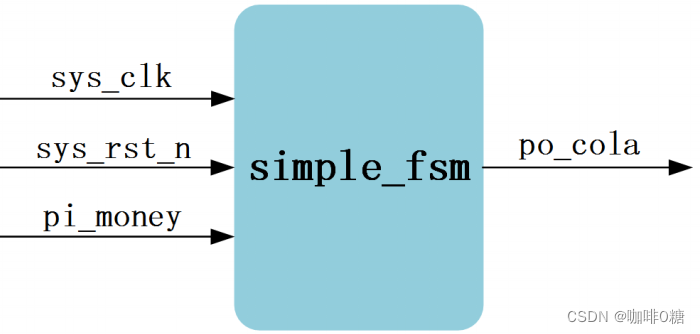

2.1 模块框图

2.2 状态转换图和波形图

2.3 RTL代码

`timescale 1ns/1ns

module simple_fsm

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire pi_money ,

output reg po_cola

);

//状态编码

parameter IDLE = 4'b0001 ;

parameter ONE = 4'b0010 ;

parameter TWO = 4'b0100 ;

parameter THREE = 4'b1000;

reg [3:0] state;

//第一段状态机,描述当前状态state如何根据输入跳转到下一状态

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

state <= IDLE;

else case(state)

IDLE: if(pi_money == 1'b1)

state <= ONE;

else

state <= IDLE;

ONE : if(pi_money == 1'b1)

state <= TWO;

else

state <= ONE;

TWO : if(pi_money == 1'b1)

state <= THREE;

else

state <= TWO;

THREE: if(pi_money == 1'b1)

state <= ONE;

else

state <= IDLE;

default : state <= IDLE;

endcase

//第二段状态机,描述当前状态state和输入pi_money如何影响po_cola输出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

po_cola <= 1'b0;

else if((state == TWO) && (pi_money == 1'b1))

po_cola <= 1'b1;

else

po_cola <= 1'b0;

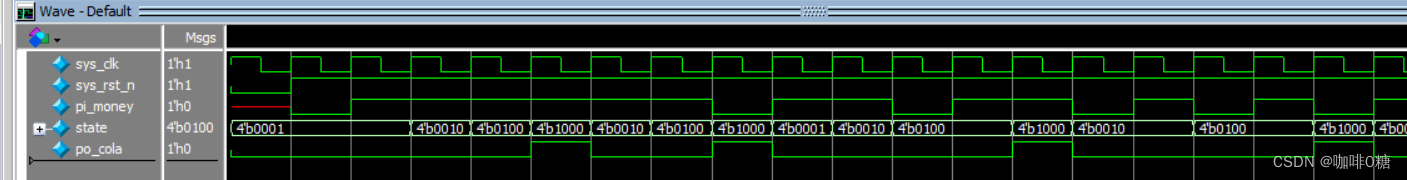

endmodule2.4 验证

仿真代码:

`timescale 1ns/1ns

module tb_simple_fsm();

reg sys_clk;

reg sys_rst_n;

reg pi_money;

wire po_cola;

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

always #20 pi_money <= {$random} % 2;

//将 RTL 模块中的内部信号引入到 Testbench 模块中进行观察,我是自己在仿真中单独添加的

//wire [2:0] state = simple_fsm_inst.state;

simple_fsm simple_fsm_inst(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.pi_money (pi_money ),

.po_cola (po_cola )

);

endmodule

上板验证:

可以选择按键作一元硬币,小灯表示可乐模拟结果。

重点:熟练掌握状态机编写的设计流程、方法和格式特点。

说明:

本人使用的是野火家Xilinx Spartan6系列开发板及配套教程,以上内容如有疑惑或错误欢迎评论区指出,或者移步B站观看野火家视频教程。

开发软件:ise14.7 仿真:modelsim 10.5

如需上述资料私信或留下邮箱。

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结