您现在的位置是:首页 >技术交流 >Vivado 下 LED 流水灯实验网站首页技术交流

Vivado 下 LED 流水灯实验

目录

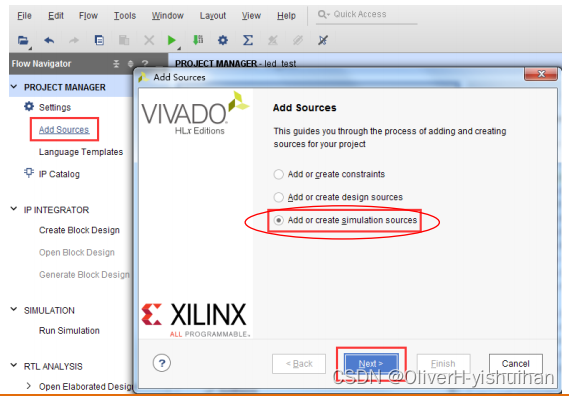

1. 点击 Project Manager 下的 Add Sources 图标(或者使用快捷键 Alt+A)。

2. 选择 Add or create design sources 选项,点击 Next。

3. 点击 Add Files 可以一个个添加源文件,点击 AddDirectories 可以按目录添加源文件。因为现在我们还没有设计程序,这里要点击 Create File 按钮。

6. 编写好代码后保存,点击菜单 File -Save All Files。

1. 点击 Project Manager 下的 Add Sources 图标。

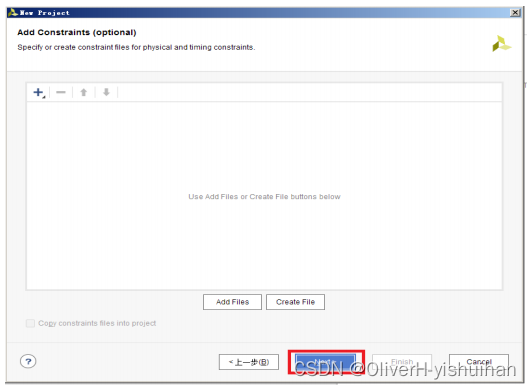

2. 选择 Add or create constraints 选项,点击 Next。

5. 双击打开这个 led.xdc 文件,在这个文件里添加以下的引脚定义。

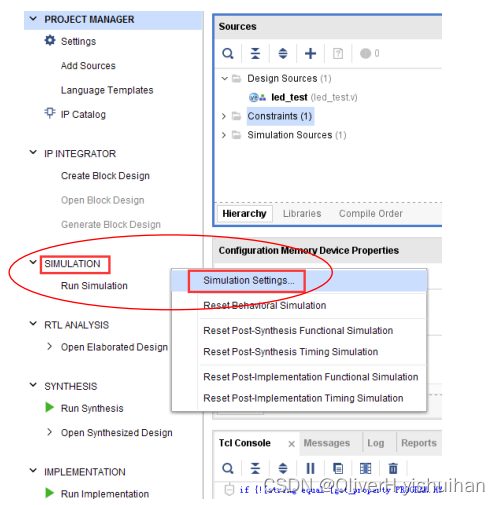

1. 设置 Vivado 的仿真配置,右击 SIMULATION 中 Simulation Settings。

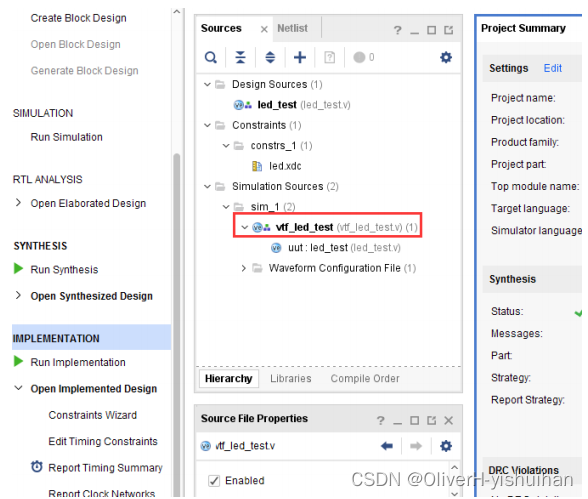

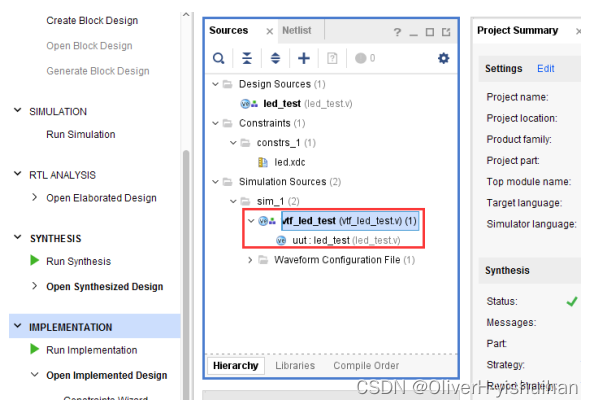

8. 编写好后保存,vtf_led_test.v 自动成了这个仿真 Hierarchy 的顶层了,它下面是设计文件 led_test.v。

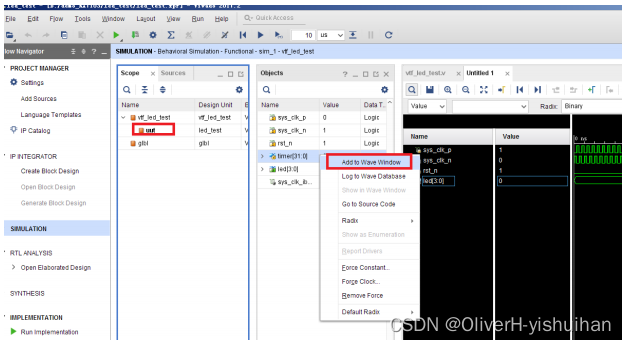

10. 在弹出仿真界面后如下图,界面是仿真软件自动运行到仿真设置的 50ms 的波形。

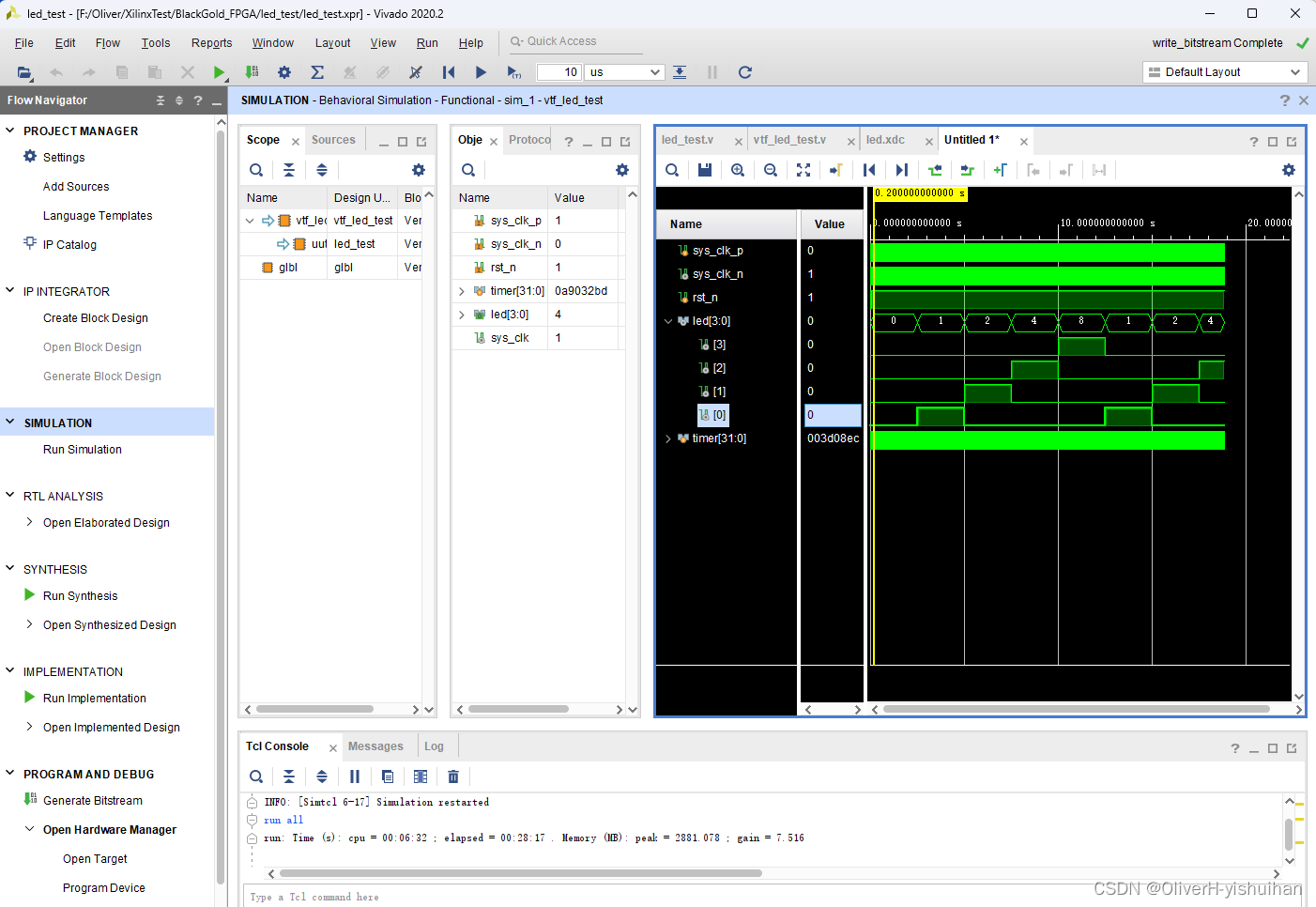

11. 点击 Restart 按钮复位一下,再点击 Run All 按钮。(需要耐心!!!),可以看到仿真波形与 设计相符。

Vivado 下 LED 流水灯实验

1、实验简介

2、实验环境

- Windows 10 64 位

- vivado 2017.4

- Xinlinx 黑金 FPGA 开发板(AX7A035 开发板、AX7A100 开发板、AX7A200 开发板)

3、实验原理

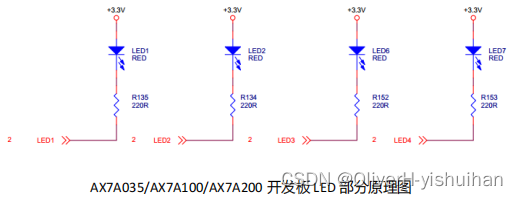

3.1、LED硬件电路

从上面的 LED 部分原理图可以看出,AX7A035/ AX7A100/ AX7A200 开发板都是将 IO 经过一个电阻和 LED 串联接电源端,FPGA 的 IO 输出低电平点亮 LED。IO 输出高电平 LED 灯熄灭,其中的串联电阻都是为了限制电流。

3.2、程序设计

//Define the time counter

reg [31:0] timer;always @(posedge sys_clk or negedge rst_n) begin

if (~rst_n)

timer <= 32'd0;

else if (timer == 32'd199_999_999)

timer <= 32'd0;

else

timer <= timer + 1'b1;

end// LED control

always@(posedge sys_clk or negedge rst_n) begin

if (~rst_n)

led <= 4'b0000;

else if (timer == 32'd49_999_999)

led <= 4'b0001;

else if (timer == 32'd99_999_999)

led <= 4'b0010;

else if (timer == 32'd149_999_999)

led <= 4'b0100;

else if (timer == 32'd199_999_999)

led <= 4'b1000;

end4、Vivado 工程

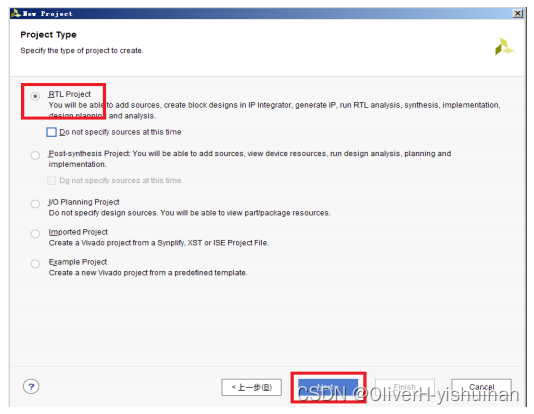

4.1、创建工程

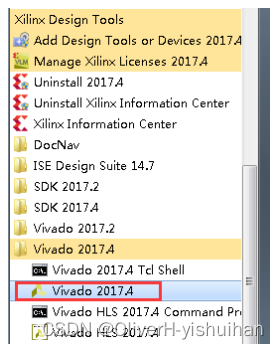

2. 在 Vivado 2017.4 开发环境里双击 Create Project,如下图:

3. 弹出一个 Vivado 的工程向导,点击 Next 按钮。

4. 在弹出的对话框中输入工程名和工程存放的目录,这里取一个 led_test 的工程名,点击 Next。

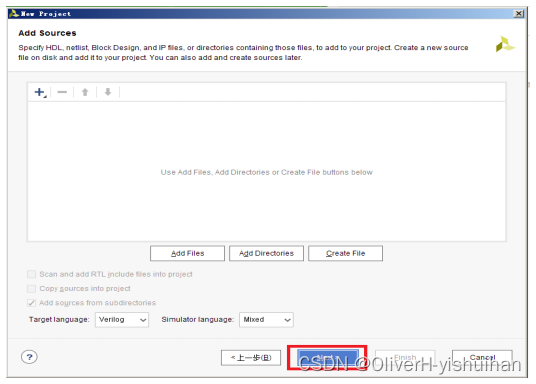

6. 进入添加 source file 界面,这里先不添加任何设计文件。点击 Next

7. 提示是否添加已有的约束文件,这里约束文件我们也没有设计好,也不添加。

8.选择所用的 FPGA 器件

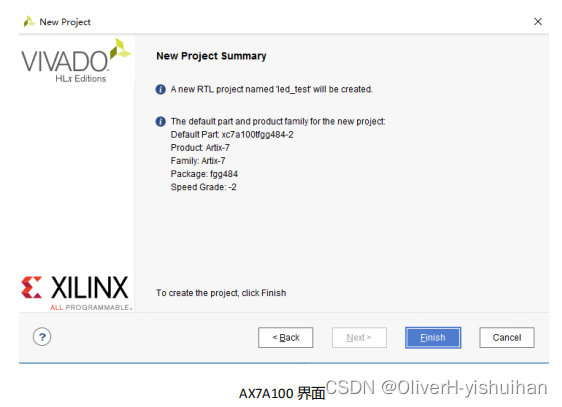

9. 再次确认一下板子型号有没有选对, 没有问题再点击“Finish”完成工程创建。

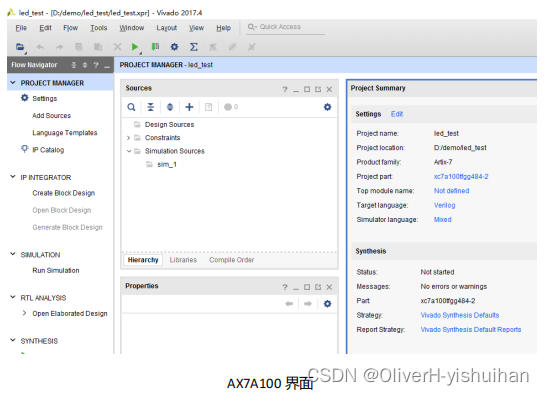

10. 工程创建后如下图所示:

4.2、编写流水灯的 verilog代码

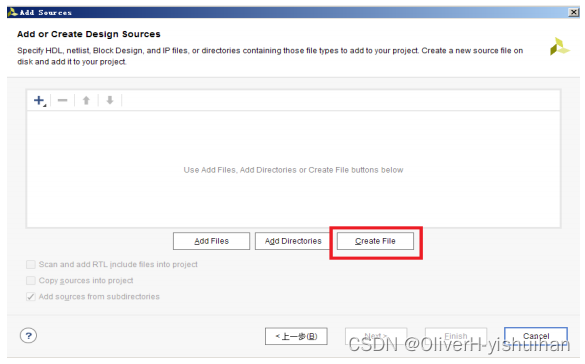

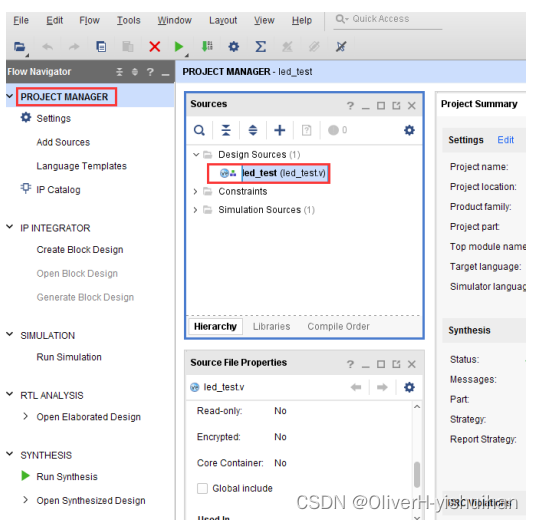

1. 点击 Project Manager 下的 Add Sources 图标(或者使用快捷键 Alt+A)。

2. 选择 Add or create design sources 选项,点击 Next。

3. 点击 Add Files 可以一个个添加源文件,点击 AddDirectories 可以按目录添加源文件。因为现在我们还没有设计程序,这里要点击 Create File 按钮。

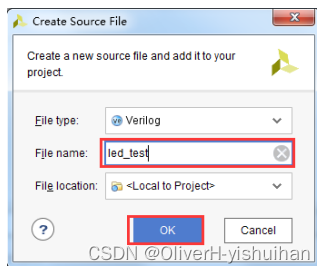

在弹出的对话框里选择 File type 是 verilog, File name 为 led_test, 点击 OK 按钮。

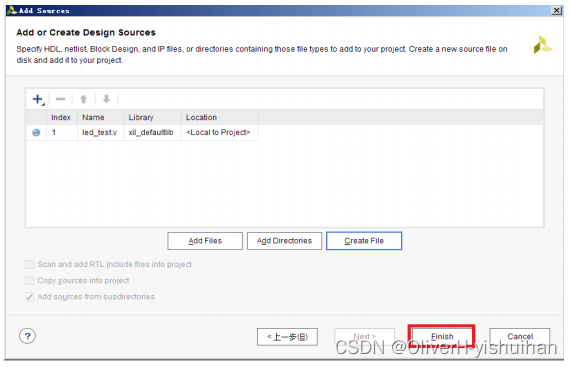

4.点击“Finish”完成。

这时在 Project Manager 界面下的 Design Sources 里已经有了一个 led_test.v 文件, 并且自动成为项目的顶层(Top)模块了。

5. 编写 led_test.v 的程序

编写 led_test.v 的程序,这里我们定义了一个 32 位的寄存器 timer, 用于循环计数 0~199_999_999(1 秒钟), 当计数到 49_999_999(0.25 秒)的时候,熄灭第一个 LED 灯;当计数到 99_999_999(0.5 秒)的时候,熄灭第二个 LED 灯;当计数到 149_999_999(0.75 秒)的时候,熄灭 第三个 LED 灯;当计数到 199_999_999(1 秒)的时候,熄灭第四个 LED 灯,计数器再重新计数。 具体的操作直接看代码吧。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/03/20 21:39:15

// Design Name:

// Module Name: led_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module led_test(

//Differential system clocks

sys_clk_p, //system clock positive

sys_clk_n, //system clock negative

rst_n, // reset ,low active

led // LED,use for control the LED signal on board

);

//===========================================================================

// PORT declarations

//===========================================================================

input sys_clk_p;

input sys_clk_n;

input rst_n;

output [3:0] led;

//define the time counter

reg [31:0] timer;

reg [3:0] led;

wire sys_clk;

IBUFDS sys_clk_ibufgds

(

.O (sys_clk ),

.I (sys_clk_p ),

.IB (sys_clk_n )

);

//===========================================================================

// cycle counter:from 0 to 1sec

//===========================================================================

always @(posedge sys_clk or negedge rst_n)

begin

if (~rst_n)

timer <= 32'd0; // when the reset signal valid,time counter clearing

else if (timer == 32'd199_999_999) //1 seconds count(200M-1=199999999)

timer <= 32'd0; //count done,clearing the time counter

else

timer <= timer + 1'b1; //timer counter = timer counter + 1

end

//===========================================================================

// LED control

//===========================================================================

always @(posedge sys_clk or negedge rst_n)

begin

if (~rst_n)

led <= 4'b0000; //when the reset signal active

else if (timer == 32'd49_999_999) //time counter count to 0.25 sec,LED1 lighten

led <= 4'b0001;

else if (timer == 32'd99_999_999) //time counter count to 0.5 sec,LED2lighten

begin

led <= 4'b0010;

end

else if (timer == 32'd149_999_999) //time counter count to 0.75 sec,LED3 lighten

led <= 4'b0100;

else if (timer == 32'd199_999_999) //time counter count to 1 sec,LED4 lighten

led <= 4'b1000;

end

endmodule

6. 编写好代码后保存,点击菜单 File -Save All Files。

4.3、添加 XDC管脚约束文件

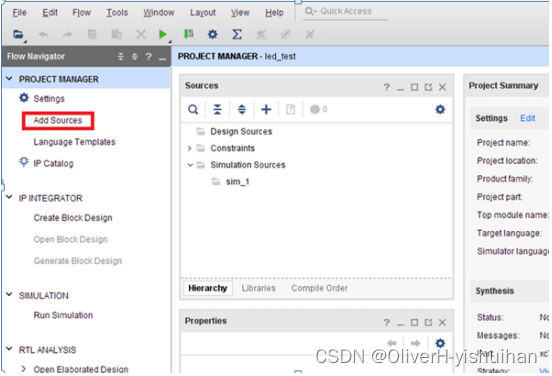

1. 点击 Project Manager 下的 Add Sources 图标。

2. 选择 Add or create constraints 选项,点击 Next。

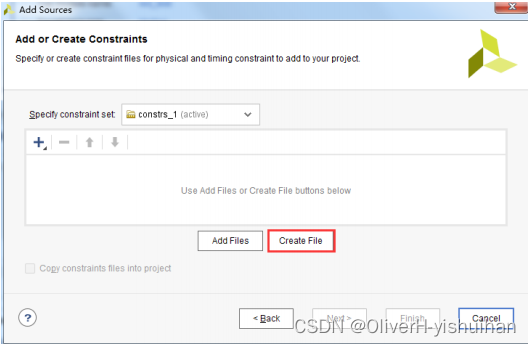

3. 点击 Create File 按钮。

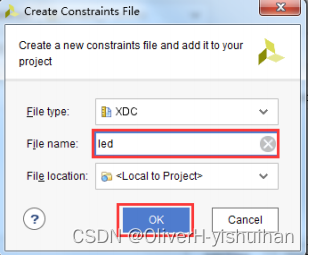

在弹出的对话框里选择 File type 是 XDC, File name 为 led, 点击 OK 按钮。

4.点击“Finish”完成。

这时在 Project Manager 界面下的 Constraints 目录的 constrs_1 目录下已经有了一个 led.xdc 文件。

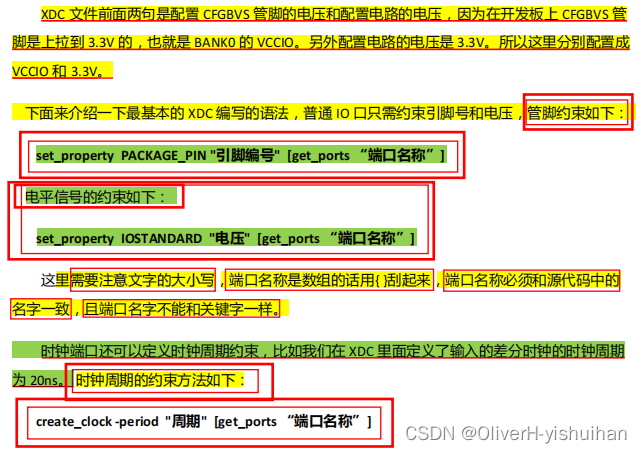

5. 双击打开这个 led.xdc 文件,在这个文件里添加以下的引脚定义。

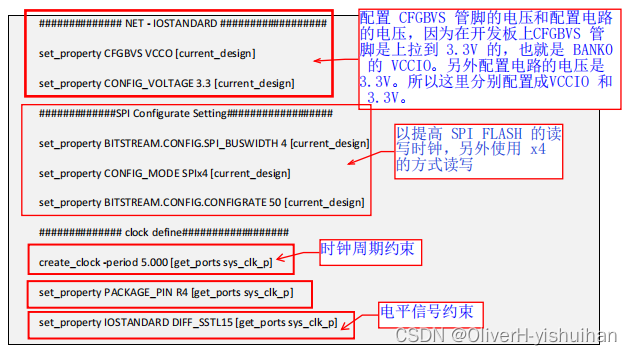

############## NET - IOSTANDARD 配置 CFGBVS 管脚的电压和配置电路的电压##################

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

############## clock define 时钟周期、时钟引脚、电平信号约束#######################

create_clock -period 5.000 [get_ports sys_clk_p]

set_property PACKAGE_PIN R4 [get_ports sys_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports sys_clk_p]

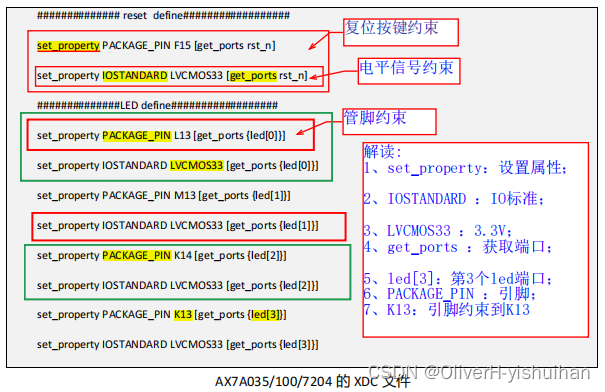

############## reset key define##########################

set_property PACKAGE_PIN F15 [get_ports rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

##############LED define############################

set_property PACKAGE_PIN L13 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN M13 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN K14 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property PACKAGE_PIN K13 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

#############SPI Configurate Setting##################

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

完成后选择菜单 File->Save all files 保存所有文件。

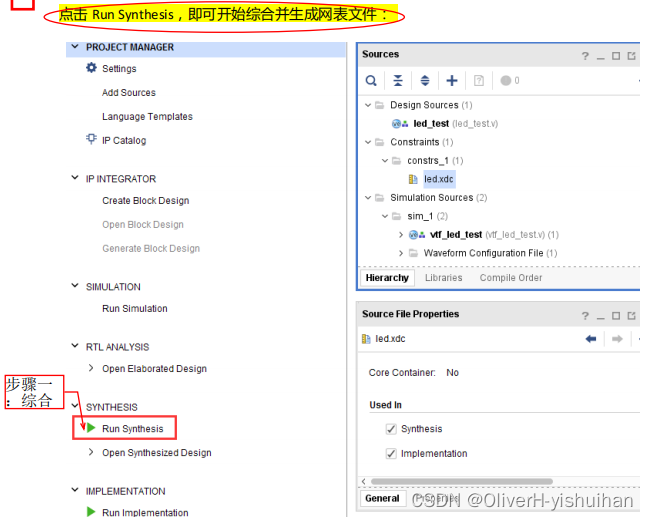

4.4、编译

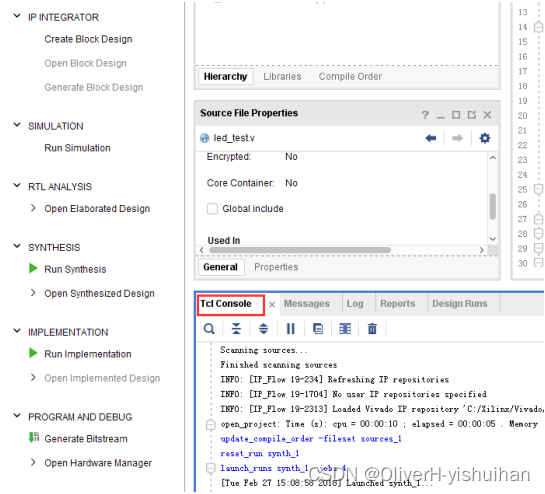

在 Tcl Console 窗口或者 Messages 窗口可以看到一些状态信息。

4.5、vivado仿真验证

1. 设置 Vivado 的仿真配置,右击 SIMULATION 中 Simulation Settings。

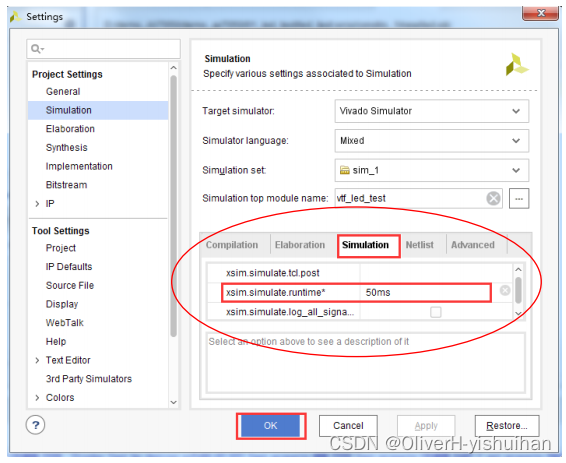

2.设置仿真时间

在 Simulation Settings 窗口中进行如下图来配置,这里设置成 50ms(根据需要自行设定),其它按 默认设置,单击 OK 完成。

3. 添加激励测试文件

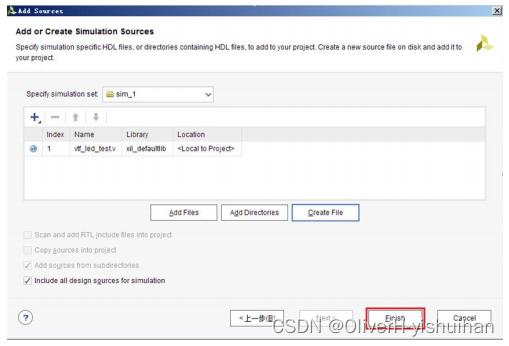

4. 点击 Create File 生成仿真激励文件。

在弹出的对话框中输入激励文件的名字,这里我们输入名为 vtf_led_test。

6. 点击 Finish 按钮返回。

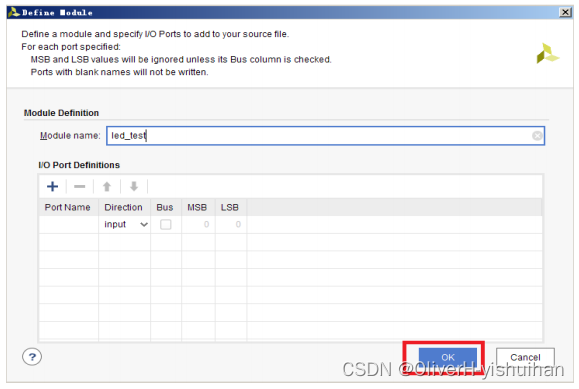

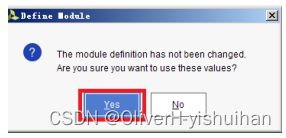

这里我们先不添加 IO Ports,点击 OK。

7.编写 vtf_led_test.v 文件的内容

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/03/20 22:45:27

// Design Name:

// Module Name: vtf_led_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module vtf_led_test();

// Inputs

//differential system clocks

reg sys_clk_p; // Differential input clock 200Mhz

wire sys_clk_n; // Differential input clock 200Mhz

reg rst_n; //reaet, low active

// Outputs

wire [3:0] led;

// Instantiate the Unit Under Test (UUT)

led_test uut (

.sys_clk_p (sys_clk_p ),

.sys_clk_n (sys_clk_n ),

.rst_n (rst_n ),

.led (led )

);

initial

begin

// Initialize Inputs

sys_clk_p = 0;

rst_n = 0;

// Wait 100 ns for global reset to finish

#1000;

rst_n = 1;

// Add stimulus here

#20000;

// $stop;

end

always #25 sys_clk_p = ~ sys_clk_p; //5ns 一个周期,产生 200MHz 时钟源

assign sys_clk_n=~sys_clk_p;

endmodule

8. 编写好后保存,vtf_led_test.v 自动成了这个仿真 Hierarchy 的顶层了,它下面是设计文件 led_test.v。

9.进行功能仿真

如果没有错误,Vivado 中的仿真软件开始工作了。

10. 在弹出仿真界面后如下图,界面是仿真软件自动运行到仿真设置的 50ms 的波形。

11. 点击 Restart 按钮复位一下,再点击 Run All 按钮。(需要耐心!!!),可以看到仿真波形与 设计相符。

4.6 下载和调试

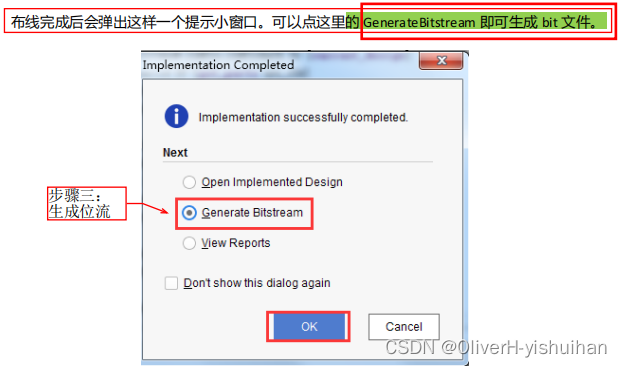

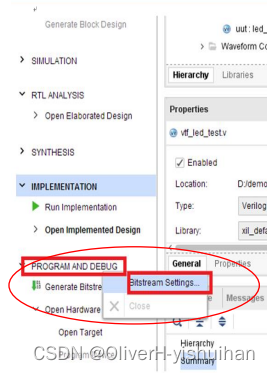

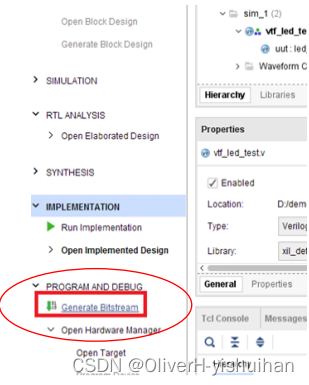

设置完成后单击 Generate Bitstream 产生中 bit 和 bin 文件。

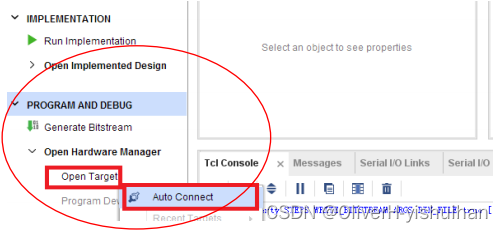

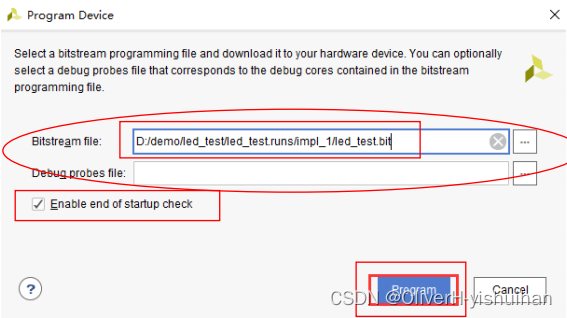

右键选择 xc7a100t_0,在弹出的选项里选择 Program Device 项。

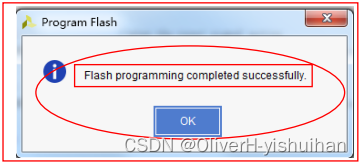

4.7、FLASH 程序固化

注意:发现此项变为灰色不能选,是因为工程中已经选有 FLASH 配置,不用再添加 flash,如下:

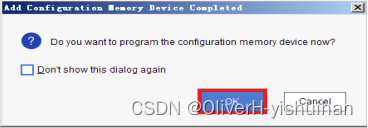

2. 在 Add configruation Memory Device 的配置界面里选择正确的 FLASH 型号,如下图所示:

#############SPI Configurate Setting##################

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]注意:在定义寄存器时,如果寄存器在 always 块里使用必须定义为 reg 类型,如果仅是用于

连线或是直接赋值需定义为 wire 类型,输入信号的类型不能定义为 reg 型,不管是 reg 类型信号

还是 wire 类型的信号,定义的寄存器宽度必须满足使用时的需要,但必须稍大于或等于需要使用

的位宽。若定义寄存器位宽远远大于使用需求则会浪费资源,如果定义的位宽小于使用需求,则

会造成数据位截断,导致程序错误。还有其他信号的类型及用法请大家参考 Verilog 语法教程。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结