您现在的位置是:首页 >学无止境 >Vivado HLS 第1讲 软件工程师该怎么了解FPGA架构网站首页学无止境

Vivado HLS 第1讲 软件工程师该怎么了解FPGA架构

简介Vivado HLS 第1讲 软件工程师该怎么了解FPGA架构

Vivado HLS是将基于C/C++描述的算法转化成相应的RTL代码,最终在FPGA上实现。这就要求软件工程师对FPGA的内部架构有一些基本的认识,目的在于保证生成的RTL代码在性能和资源上能够达到很好的平衡。实际上,C语言与FPGA是有一些对应关系的。比如:

C语言中的数组可对应于FPGA中的寄存器、分布式RAM、Block RAM或者UltraRAM

C语言中的乘加运算可对应于FPGA中的乘加运算单元(DSP48)

但不同于硬件工程师,对于FPGA内部其他资源比如高速收发器等,软件工程师可不必了解。

本讲从软件工程师的视角重点介绍FPGA内部常规逻辑单元,包括查找表(LUT)、乘加运算单元(DSP48)、存储单元(Block RAM)。这三类资源在算法开发中或多或少都会用到,在Vivado HLS的综合报告中也有所体现。

1. VIVADO HLS的设计流程

2. C/C++表述算法时的代码风格

3.FOR循环的优化方法

4.数组的优化方法

5.I/O端口的实现方式

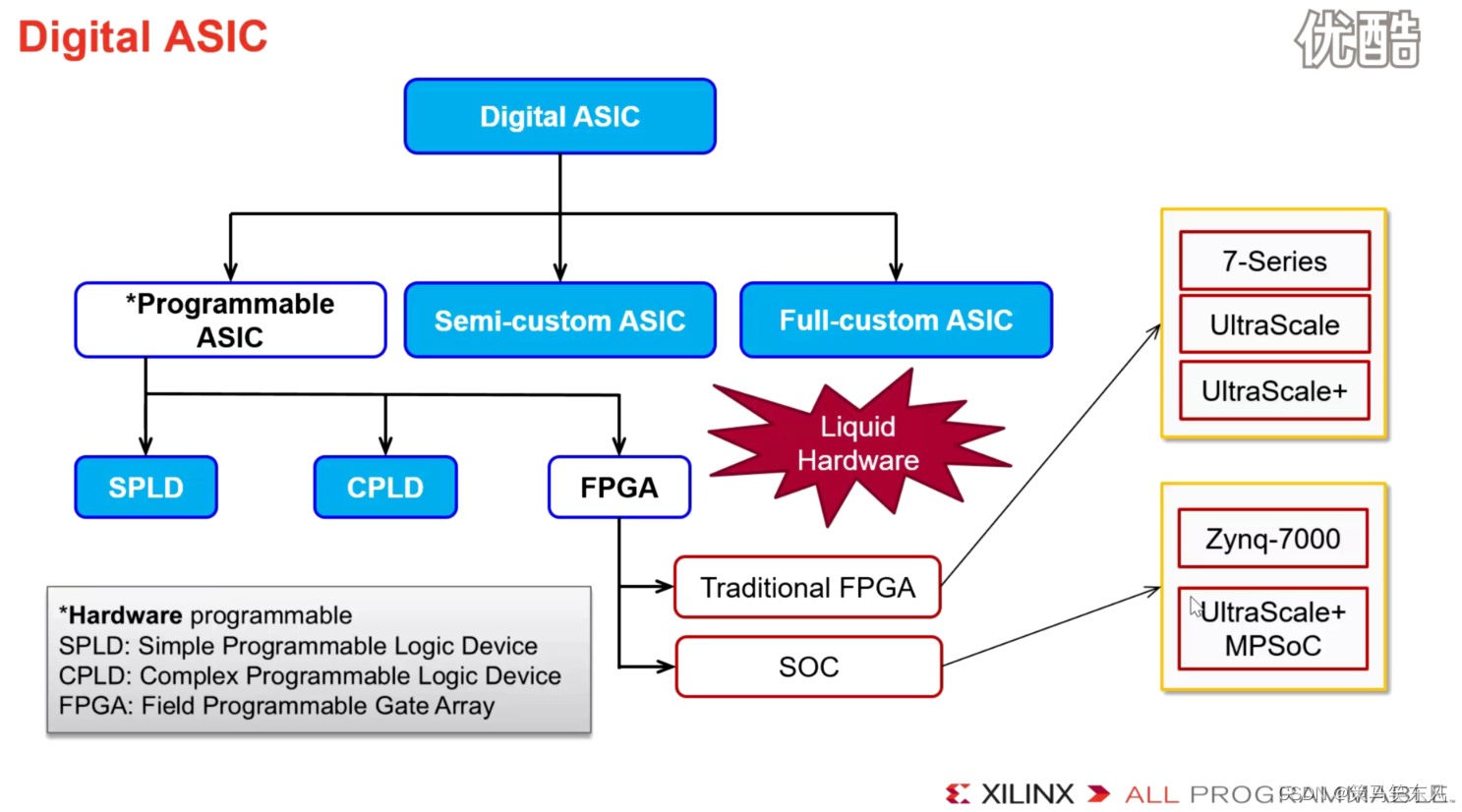

FPGA包括传统FPGA,其中包括7-series ,UltraScale,Ult

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结