您现在的位置是:首页 >技术杂谈 >【FPGA-DSP】第十期:sysgen算法封装与调用网站首页技术杂谈

【FPGA-DSP】第十期:sysgen算法封装与调用

简介【FPGA-DSP】第十期:sysgen算法封装与调用

参考视频教程第10期 - sysgen算法封装与调用 - 基于FPGA的数字信号处理系统开发笔记_哔哩哔哩_bilibili

该教程主要实现如何将sysgen编写的算法模块给实际的应用起来

添加封装有两种方式:

- 在Vivado中使用ip核添加算法模块封装

- 在Sysgen中将算法模块封装

Sysgen开发

sysgen配置如下:

注意:Compliation选择IP catalog才能实现将sysgen导出为ip核模块

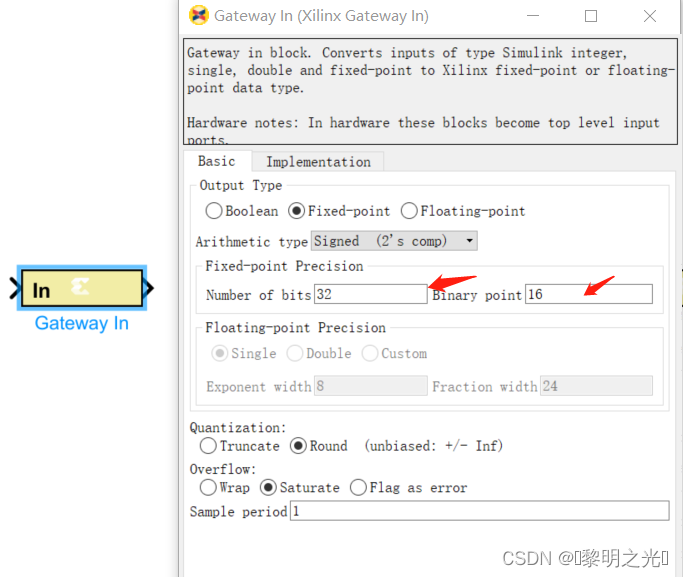

输入输出配置

| In Gateway | In Gateway |

|  |

注意:Basic一栏中bit宽度为32,小数位为16,这是必须的!因为寄存器的大小是32位。同时我们使用ip核时,接口需要设置成AXI4-lite总线,因为我们的vivado工程是使用的AXI4总线来进行开发的,所以该ip核也需要按照AXI4总线接口来开发。

简单的加法算法:

注意:加法器的输出需要修改为32位16小数,不然默认输出为33位,这会与Out Getway的位数产生冲突,同时使能端口的输入getway需要设置为布尔型 通过使能就可以控制加法模块的运行,使能为真,输出a+b,使能为假,输出0。

在设计好我们的模块之后,保存,并导出为ip_demo ip核文件

接下来我们就需要在vivado中天机啊和使用我们的ip核

接下来我们就需要在vivado中天机啊和使用我们的ip核

Vivado开发

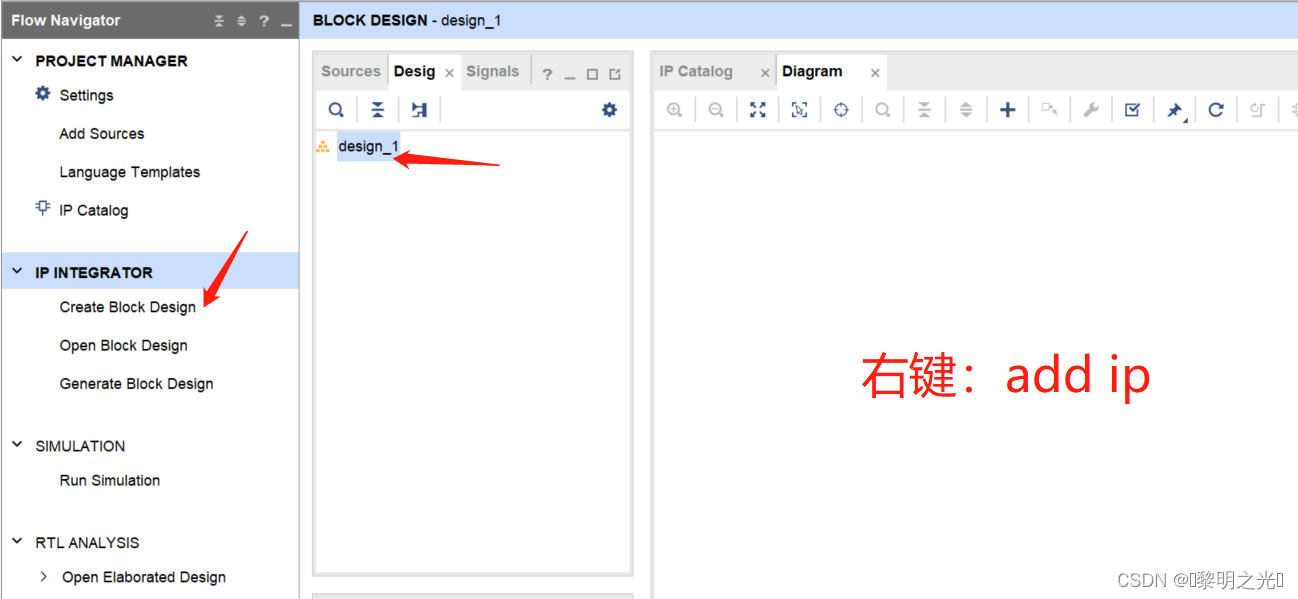

首先创建一个Block Diagram,然后在其界面中右键添加上面所创建的ip核

添加进ip仓库之后我们就可以添加自己的ip核了

添加进ip仓库之后我们就可以添加自己的ip核了

由于该IP核是满足AXI4总线协议的,因此点击run connection automation即可将我们的加法模块和我们基于AXI4的项目设计自动连接,不需要其他额外配置。

风语者!平时喜欢研究各种技术,目前在从事后端开发工作,热爱生活、热爱工作。

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。...

QT多线程的5种用法,通过使用线程解决UI主界面的耗时操作代码,防止界面卡死。... U8W/U8W-Mini使用与常见问题解决

U8W/U8W-Mini使用与常见问题解决 stm32使用HAL库配置串口中断收发数据(保姆级教程)

stm32使用HAL库配置串口中断收发数据(保姆级教程) 分享几个国内免费的ChatGPT镜像网址(亲测有效)

分享几个国内免费的ChatGPT镜像网址(亲测有效) Allegro16.6差分等长设置及走线总结

Allegro16.6差分等长设置及走线总结